System Maintenance occurs every Friday.

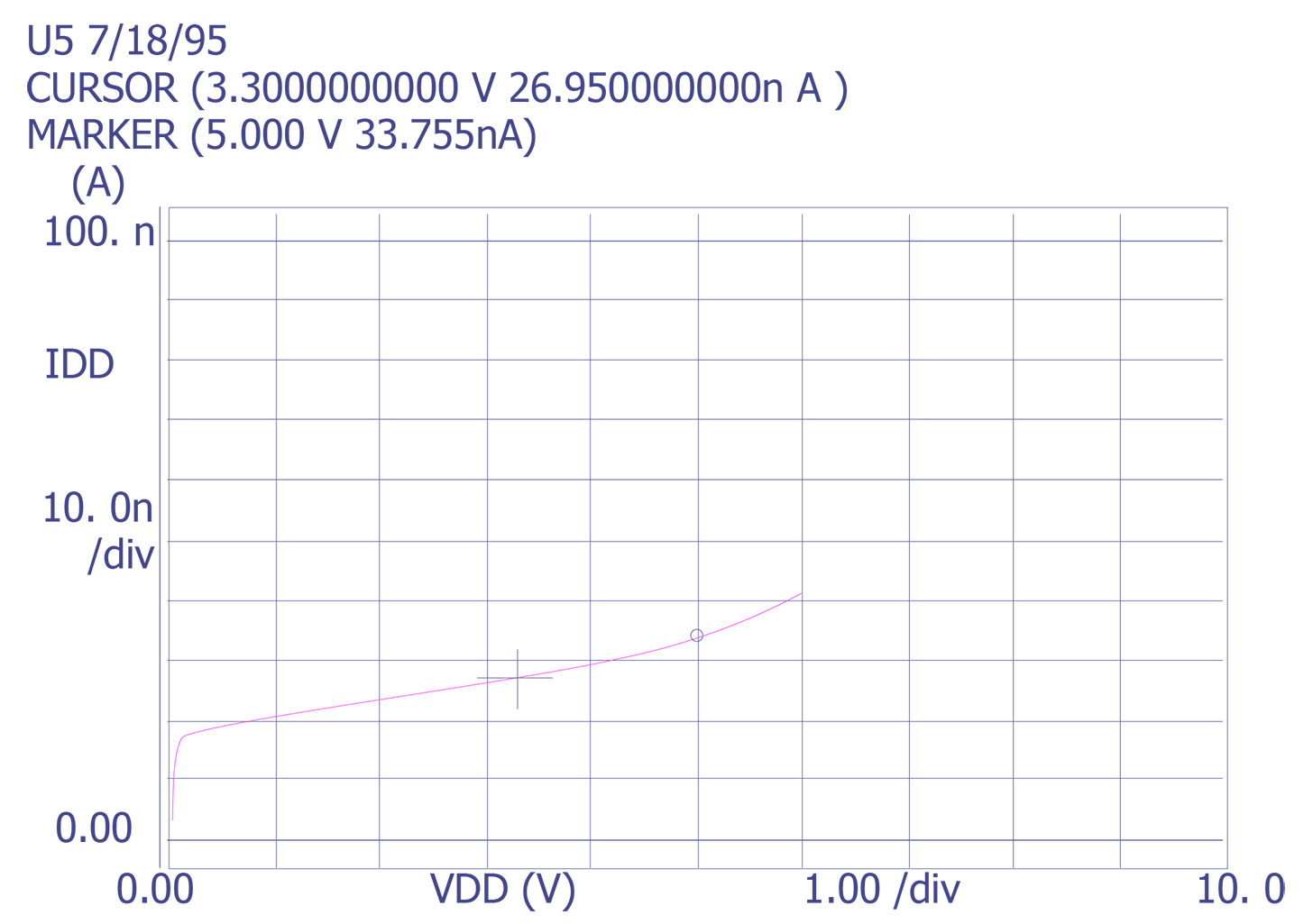

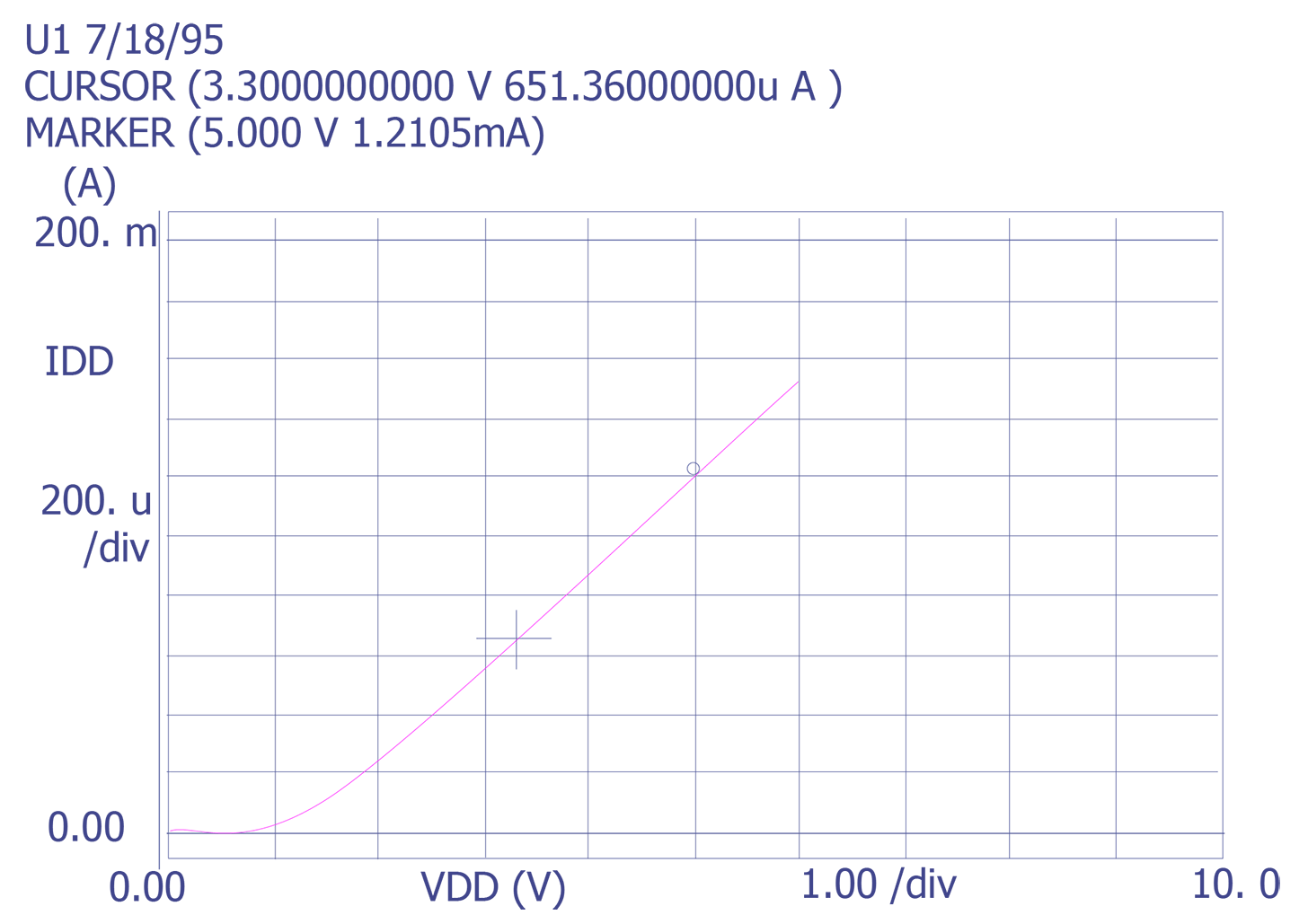

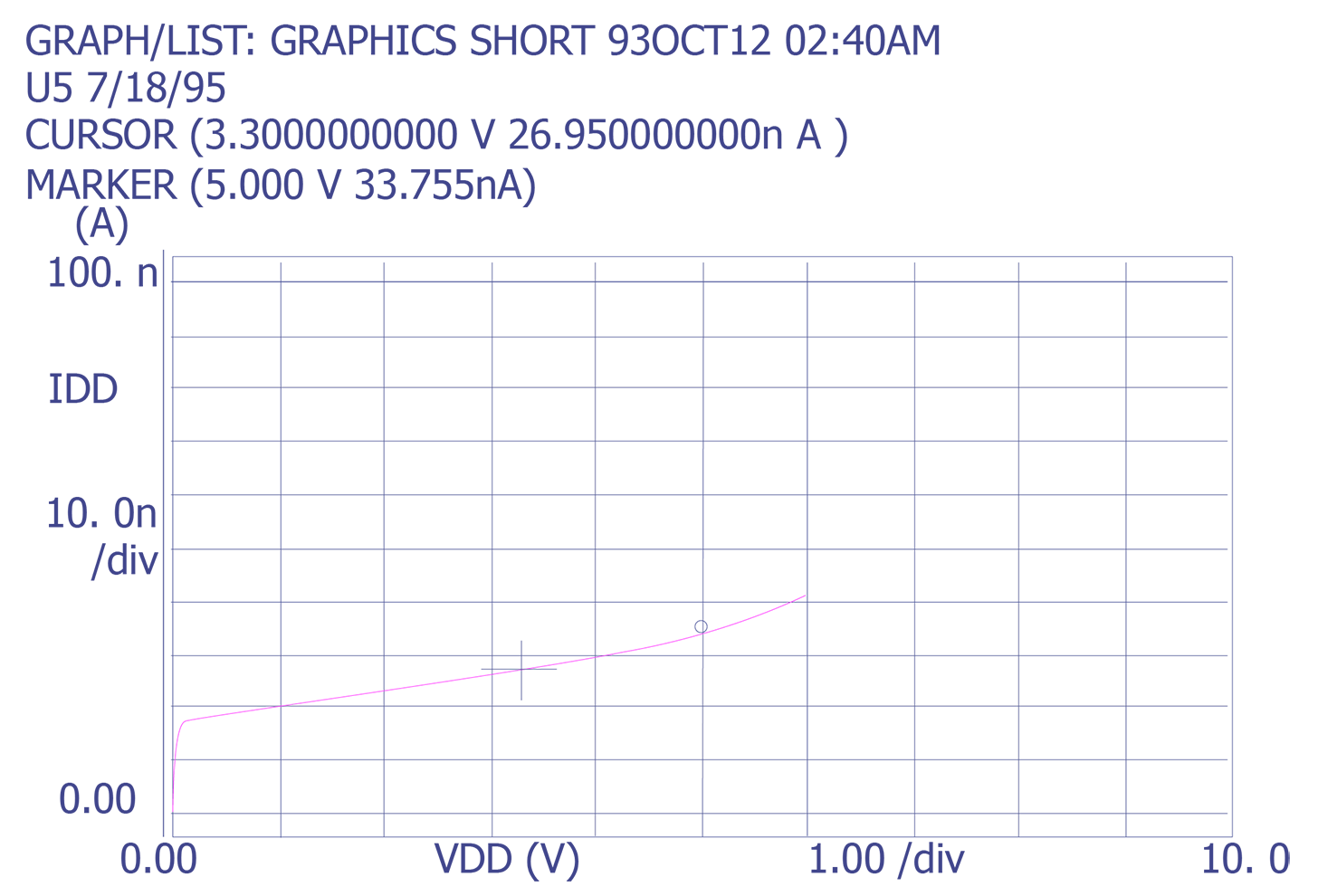

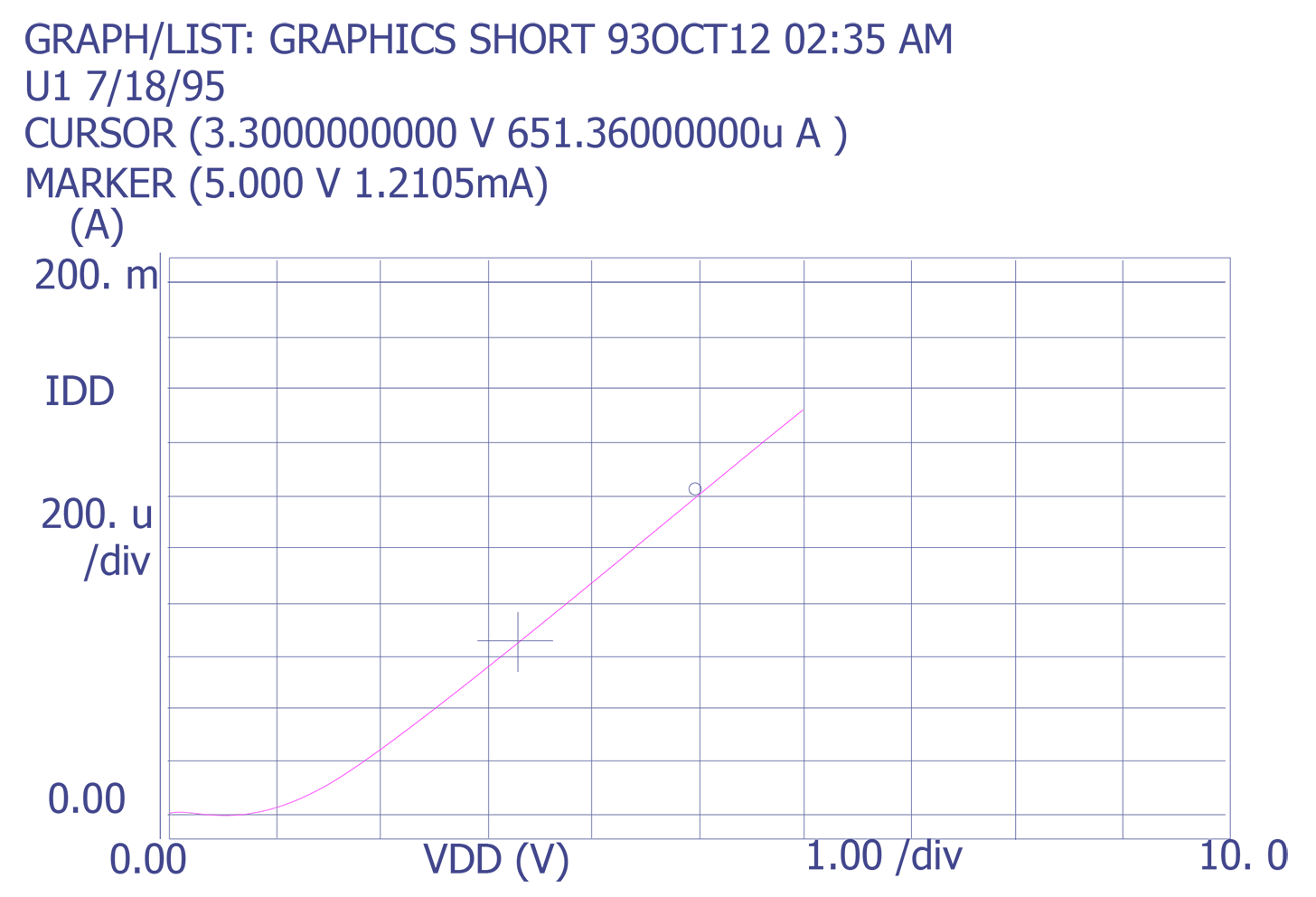

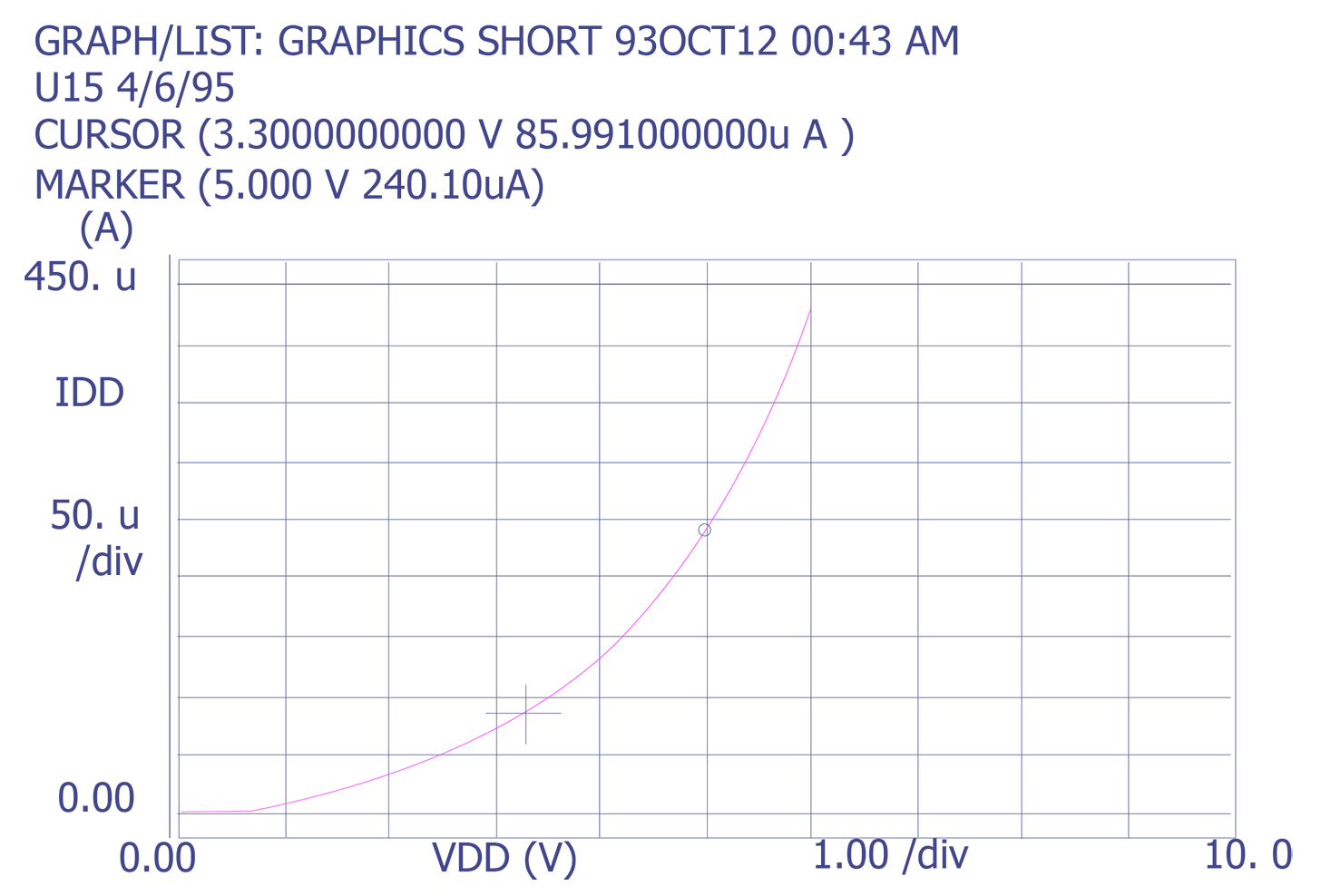

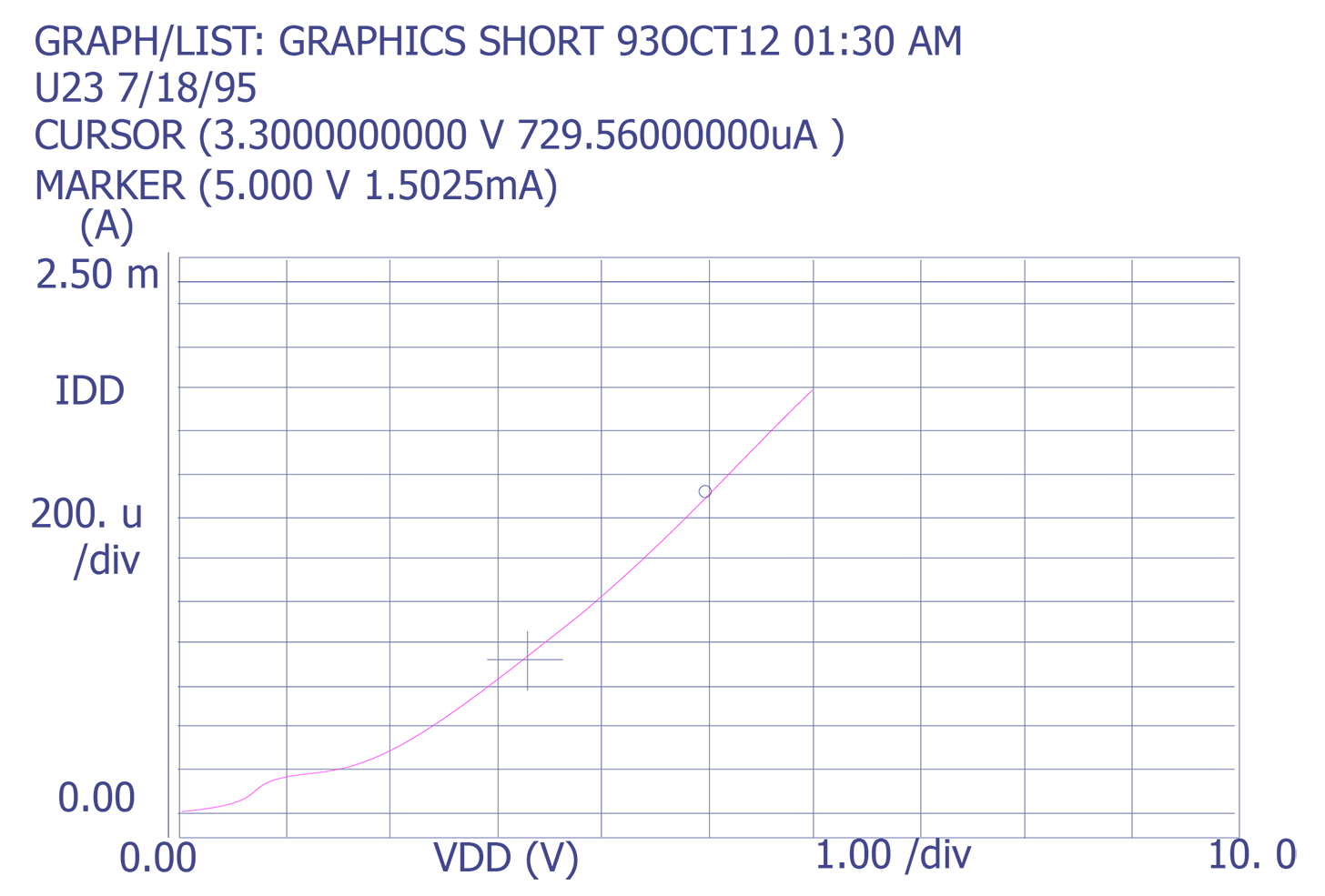

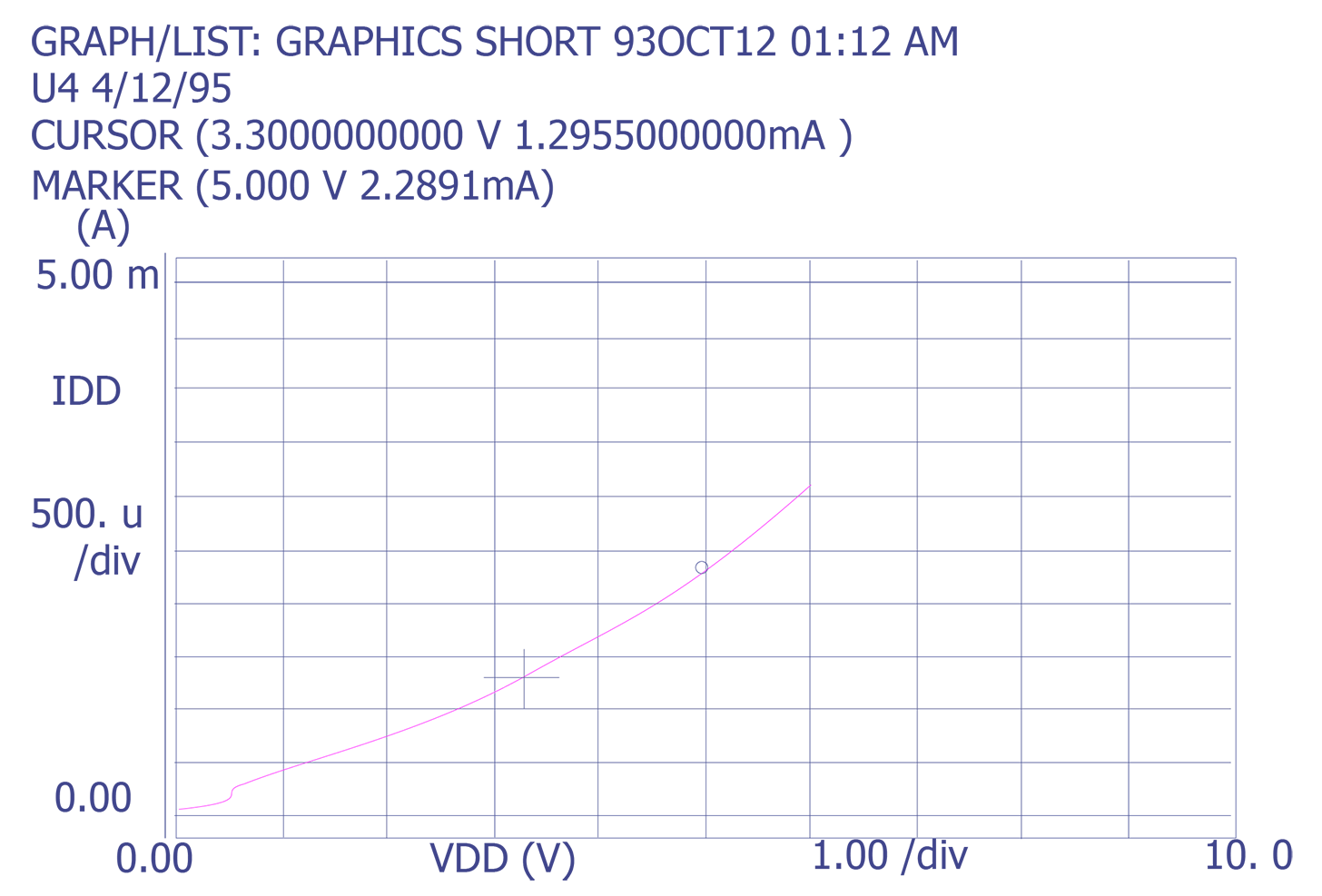

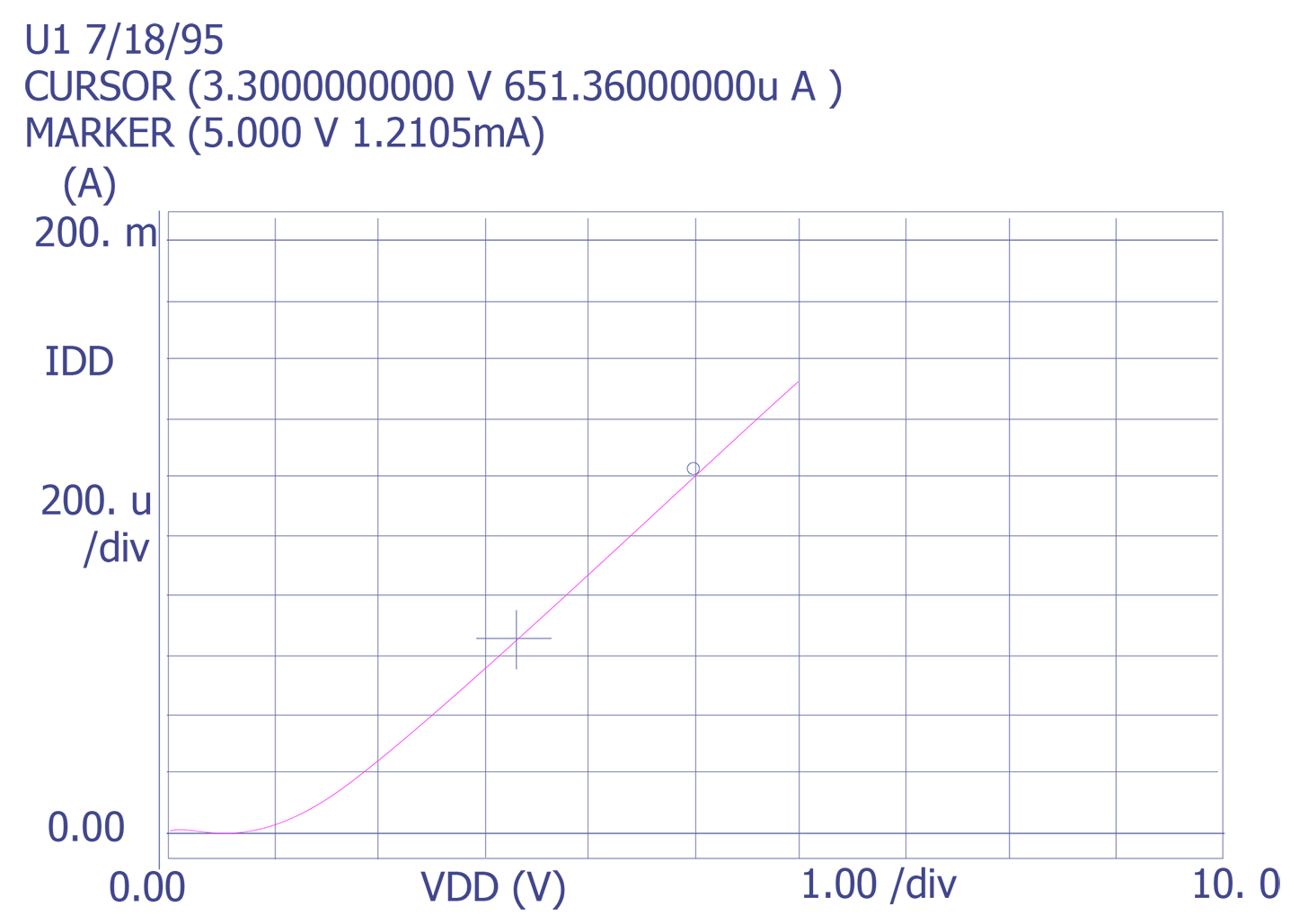

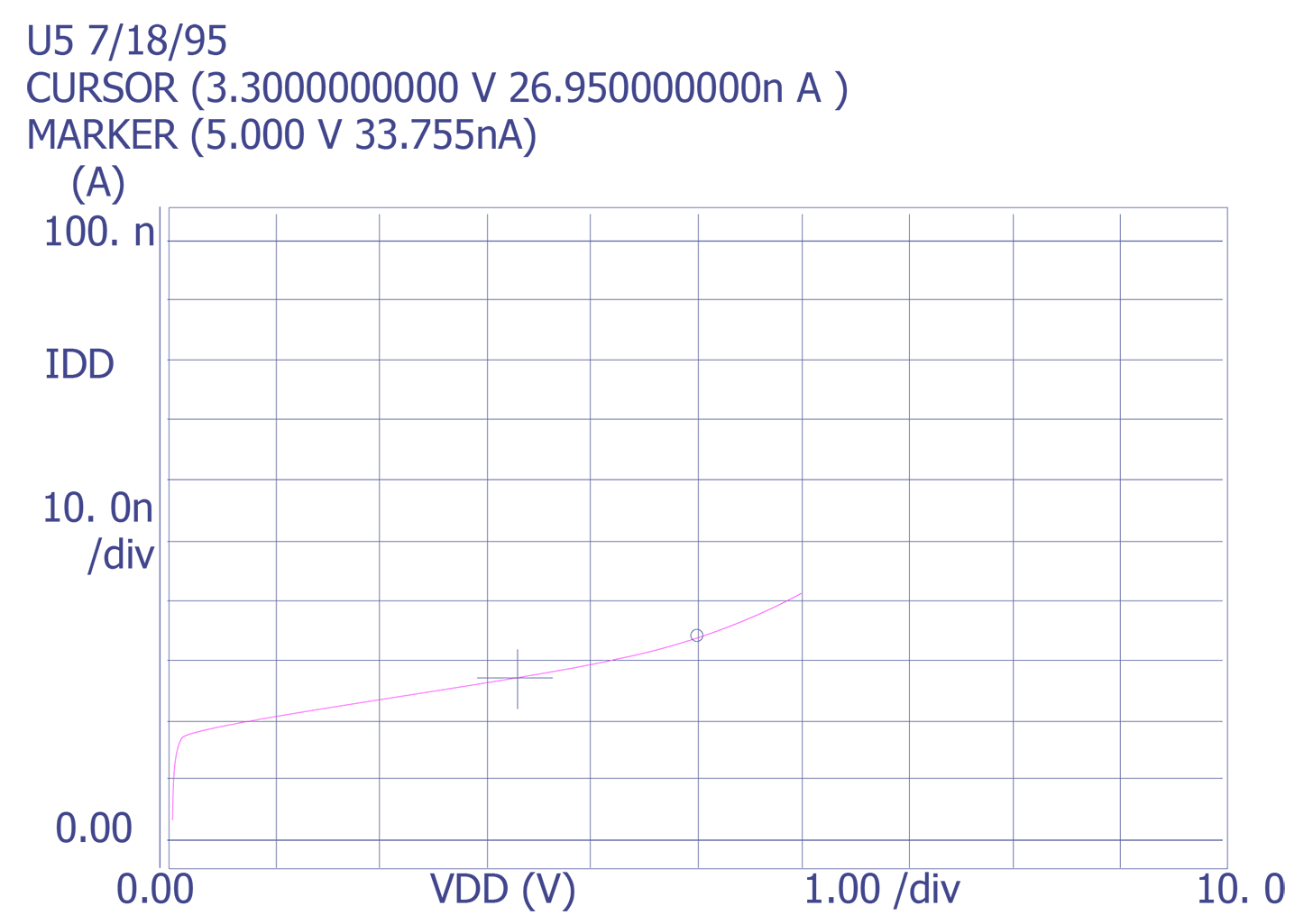

A curve trace is produced by an electrical test usually made by measuring the current (I) that results from applying a voltage (V) varied over a range from one voltage value to another value. The display or plot of current versus voltage obtained from this test is referred to as a curve trace or I-V measurement. Curve traces can also be V-V or V-I measurements. More specifically, curve trace measurements for power supply current are made across the power supply terminals (VDD and VSS or VCC and GND). Two main modes can yield useful information: current vs. voltage and current vs. time.

Current vs. voltage is the most common method for gathering data. Typically, an IC is placed in a low current state by tying the inputs to appropriate values (logical "1" or "0") and letting the output pins float. Many ICs must be initialized (i.e., placed in a state with no internal contentions) through the use of the clock pin or a vector set in order to place the IC in a low current state. Because power supply current can range over several orders of magnitude, take an initial measurement using a logarithmic scale for current if possible. Once you have examined the magnitude and general shape of the curve, take the measurements using a linear scale for current.

Current vs. time is another useful method for gaining insight into the failure mode. The IC is placed in the state in which the electrical failure mode is active. The voltage is set at the maximum operating voltage, and the current is monitored for changes during a period of several seconds to a minute.

Power supply current measurements can yield information that allows the analyst to determine the failure mechanism. The shape of the current and its stability give important clues to the presence of failure mechanisms such as gate oxide defects, inter-level shorts, metal stringers, and a variety of open interconnect failure mechanisms.

The typical curve trace test method is to force a voltage and measure the resultant current for a single pin at a time to evaluate continuity or leakage current. Curve trace I-V measurements are made with instruments such as the Tektronix 576 or HP4145 Semiconductor Parameter Analyzer. The Tektronix 576 is an analog instrument commonly used to provide a real time display of the current and voltage while the voltage continuously sweeps from a negative voltage through zero to a positive voltage and back to the negative voltage (AC mode). The HP4145 is a digital instrument that can display the current and voltage with the voltage incrementally stepped between two values. The HP4145 can provide both linear and logarithmic displays, save data in internal files and on floppy diskettes, and send data to other equipment, such as a plotter.

The most common method for measuring the power supply current is to use a switchbox to set the IC in the desired state. Once the IC is placed in the socket, check the pins for continuity. To do this, set all switches low. Connect pin 1 to the curve tracer. Sweep the voltage from -1 to +1 volts. Input, bi-directional, and output pins should exhibit diode characteristics in both directions. The VDD pin(s) should exhibit a diode characteristic in the reverse direction only, and the VSS pin(s) should exhibit a diode in the forward direction only. Once continuity has been verified, place the pins in a condition to exercise the defect. At this point during the analysis, you may not have a good indication on how to do this.

After locating a high current state, use the following procedures to characterize it. If it is relatively easy to produce the high current state, sweep the voltage from the maximum rated supply voltage down to zero volts on a logarithmic scale and repeat the measurement using a linear scale. Once this has been done, reproduce the condition using the maximum rated supply voltage and measure the current with respect to time. Measure for at least 10 seconds, and, if possible, up to 60 seconds. If the condition is difficult to reproduce, make the time measurement first and then make the current voltage sweep (max. voltage to zero) using a logarithmic scale. This will hopefully allow you to obtain the most data. If at all possible, repeat the process to confirm your initial measurements.

If you are unable to produce a high current state using a switchbox, you may be able to use Automatic Test Equipment to locate potential high current states. This requires a tester with a power supply current option and a vector set with the capability of halting on particular vectors and making measurements. The test engineer for the IC may be able to help you with this activity.

Methods for determining the high current state

With a bench setup, you may want to try the following things:

A power supply current curve trace is commonly for IDDQ vs VDD measurements for CMOS ICs. This type of measurement is preferred rather than a measurement of current at a single voltage for several reasons, including: (1) the curve trace instrument can provide more precise control over the maximum current, voltage, or power to assure that the failure mechanism is not altered and that the component is not damaged,(2) the I-V curve can provide useful information about the stability and nature of the failure mechanism.

Another important reason for performing a power supply current curve trace is the amount of information that can be obtained quickly and non-destructively. The curve can be obtained in a manner of minutes and can yield useful information on the stability and nature of the failure mechanism. Because of its relative ease to obtain, it is also useful as a monitor after each destructive step to determine if conditions have changed as a result of the step or technique.

A power supply current curve trace is usually performed as one of the initial electrical measurements during analysis of a component. While this technique is most useful for CMOS ICs, it can also be used for bipolar and BiCMOS ICs in certain instances.

Power supply current measurements would typically be used first to attempt to confirm the failure symptoms. For example, the curve can be used to confirm an IDDQ failure or standby current failure. Second, the curve can be used to determine if a functional or parametric failure has an associated high current signature. If a high current signature can be obtained, a number of rapid localization techniques can then be employed to determine the failure (i.e. liquid crystal, light emission, CIVA, LIVA, and Fluorescent Microthermographic Imaging).

A power supply curve curve trace should also be performed after tests that can alter the current demands on the IC, such as an unbiased bake and biased temperature stressing. The technique should also be performed after each destructive test such as delidding, top glass removal, backgrinding, and backside die thinning. The technique is a quick and easy way to determine if the destructive step altered the behavior of the IC.

MIL STD Procedures for Power Supply Current

MIL-STD-883C

METHOD 3005.1

POWER SUPPLY CURRENT