System Maintenance occurs every Friday.

Device recognition is the correlation of schematic elements to physical layout structures on the IC. For example, the analyst might need to determine if a particular defect is occurring in a NAND gate or in a D flip-flop. The analyst accomplishes this task by determining what combination of layers implement what devices, building up these individual identifications into a circuit or portion of a circuit.

Device recognition is a useful and many times necessary skill for the failure analyst when he or she is required to relate a physical defect to a particular electrical behavior. Device recognition may also be necessary when layout and schematic information are not available. The skill of correlating a schematic element or elements to physical structures on the IC can mean the difference between properly identifying the failure mechanism and misdiagnosis.

Device recognition is performed for several different reasons:

These four reasons constitute the main reasons for performing device recognition. A proficient analyst should be able to produce a schematic from layout data or optical/SEM inspection coupled with some deprocessing.

Device recognition is typically performed using an optical microscope. Some of today's more advanced technologies require deprocessing and SEM inspection as well. Many regard device recognition as a black art. While today's complex designs can make device recognition difficult, a basic understanding of VLSI design and processing can make this task relatively straightforward. First, a basic understanding of processing is in order.

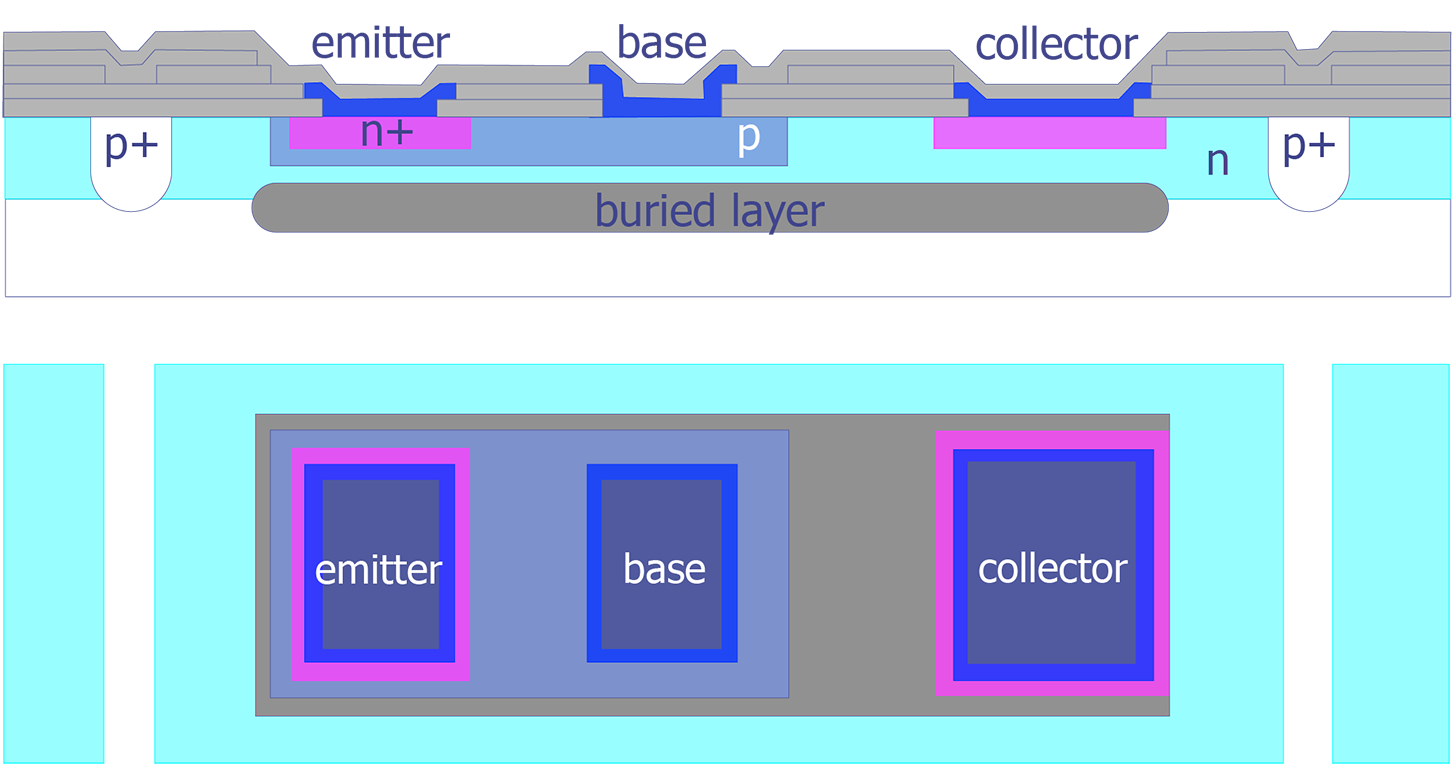

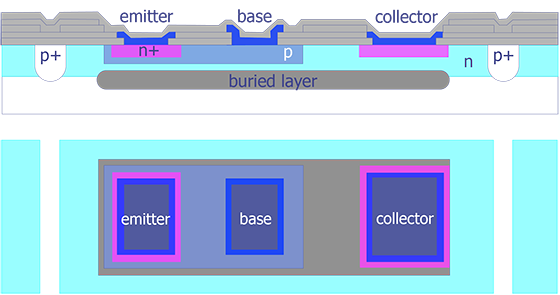

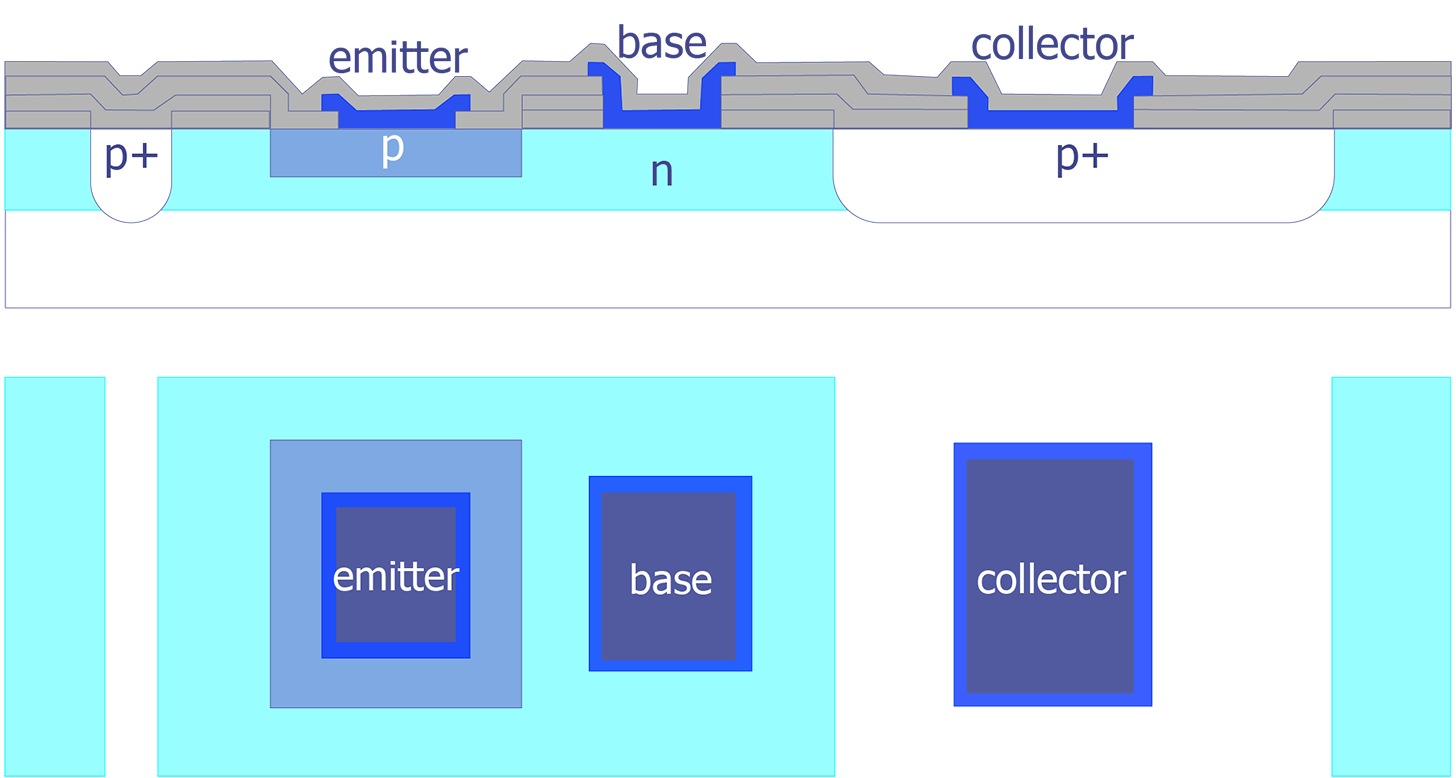

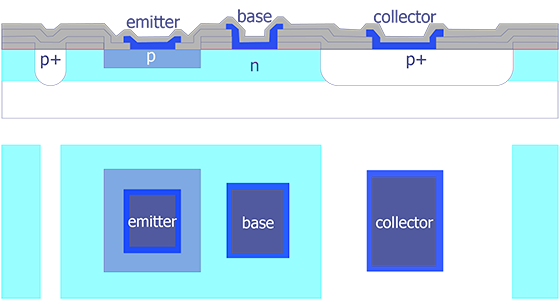

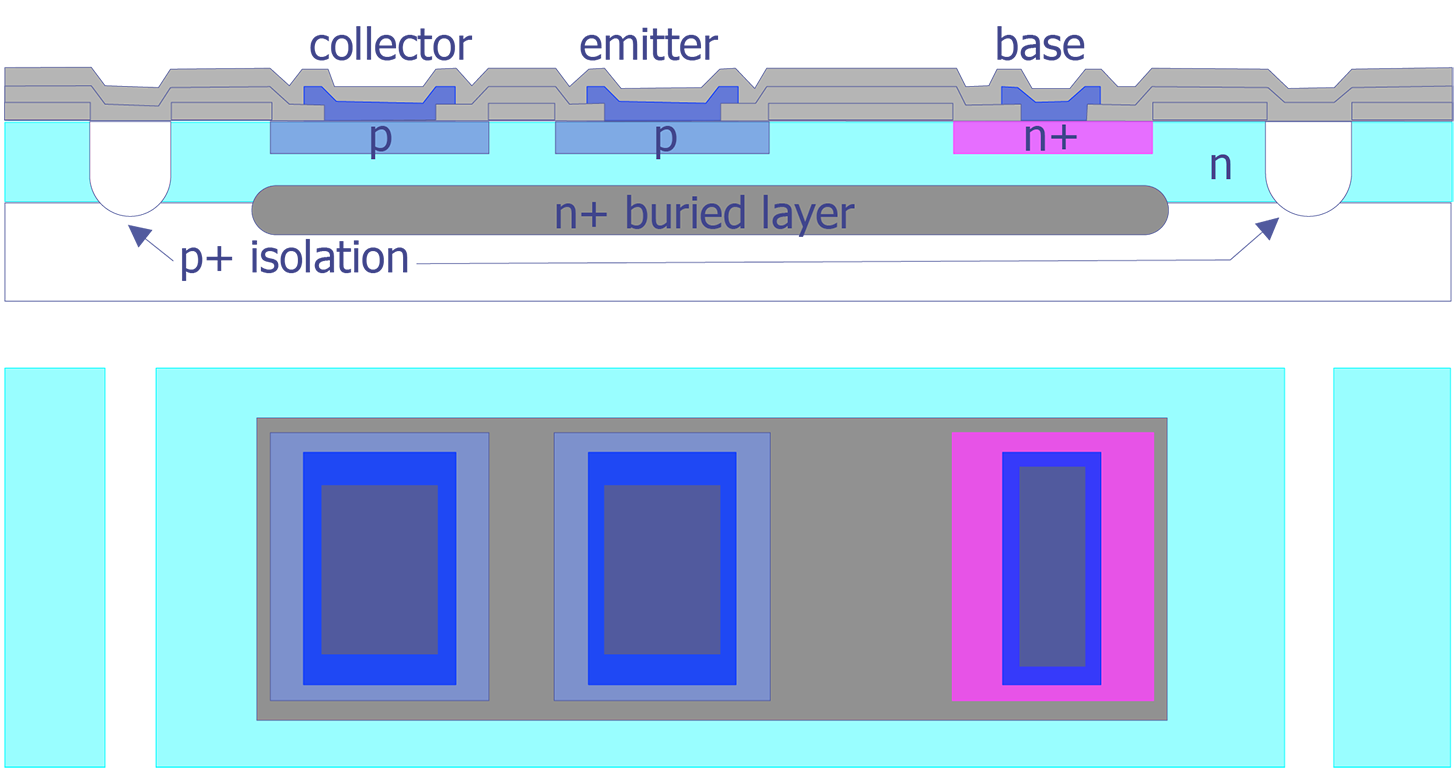

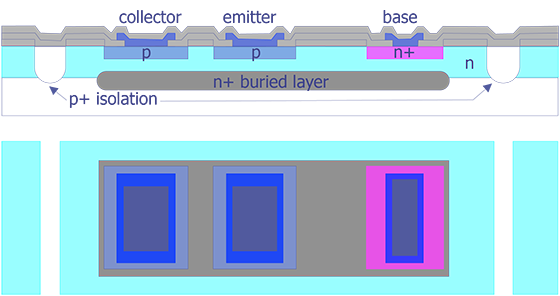

A typical npn bipolar transistor has the following appearance in cross section and top view (see Figure 1). Again, the cross sectional and top view coincide in the horizontal dimension. A substrate pnp bipolar transistor is shown in Figure 2. Although the current gains from this design can be made relatively high, the collector terminal is connected to the substrate, limiting its use in potential designs. Another common pnp transistor design is the lateral pnp transistor (see Figure 3). This transistor has relatively poor transistor gain since the base diffusion is larger. However, it does allow for more flexibility in design.

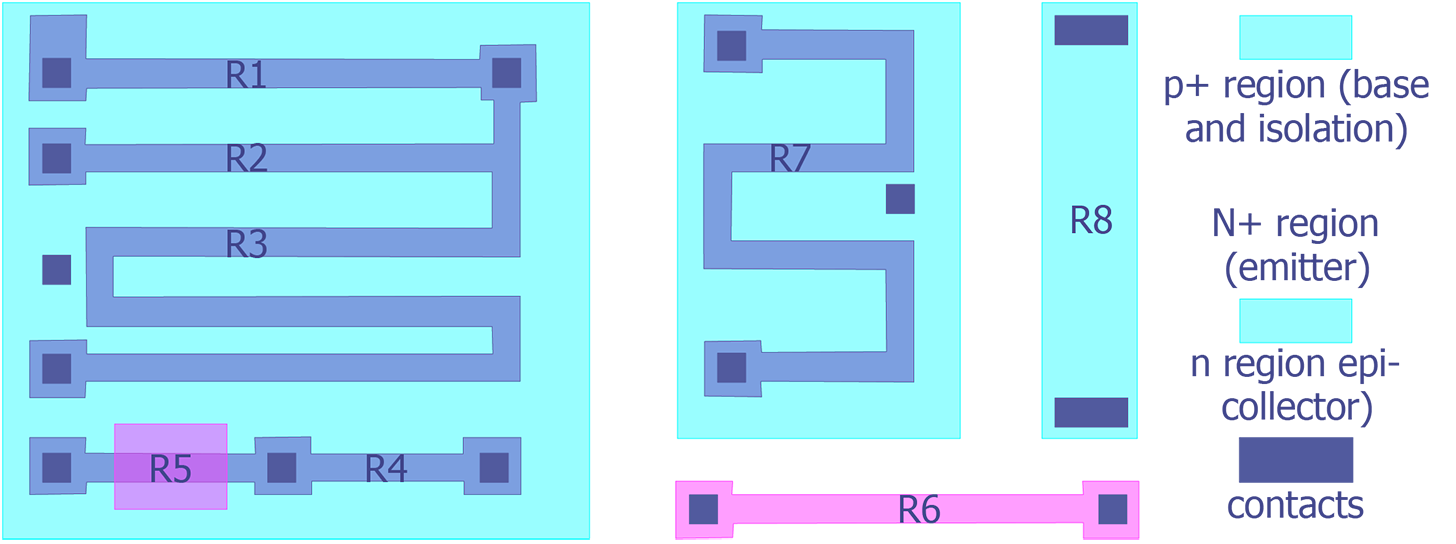

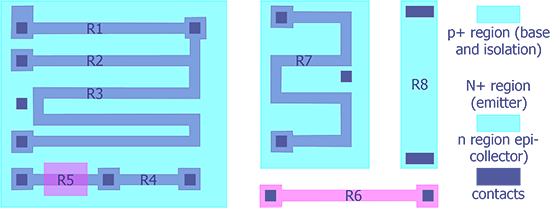

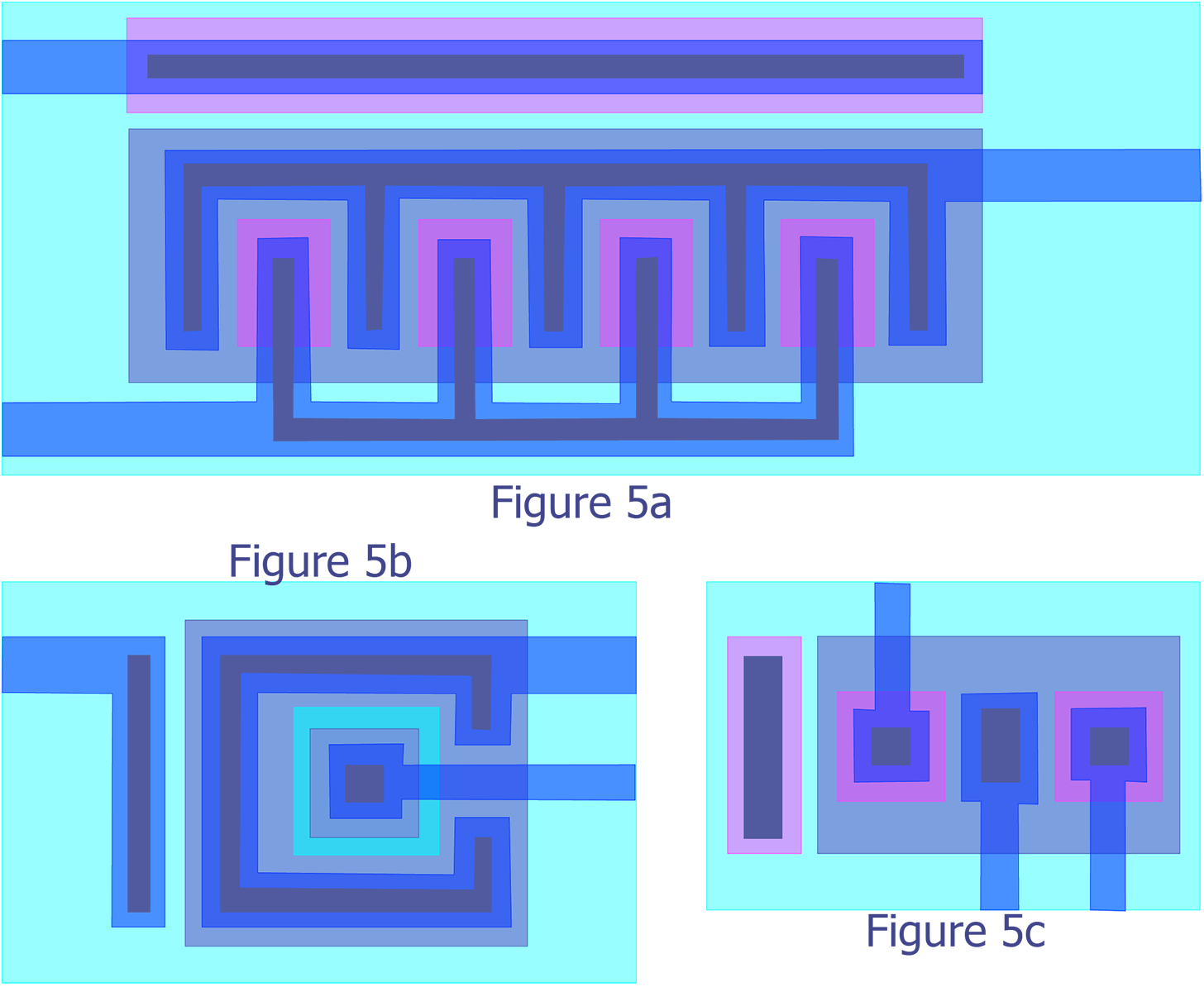

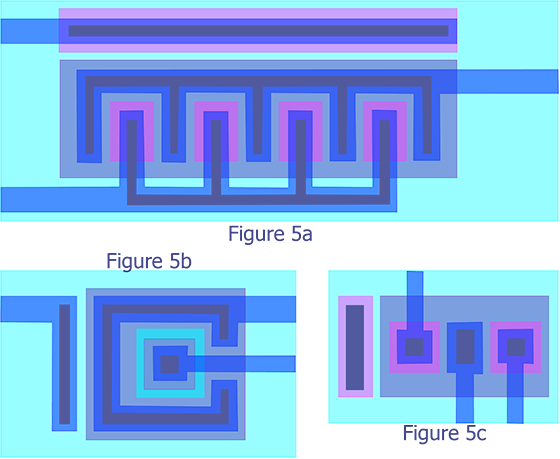

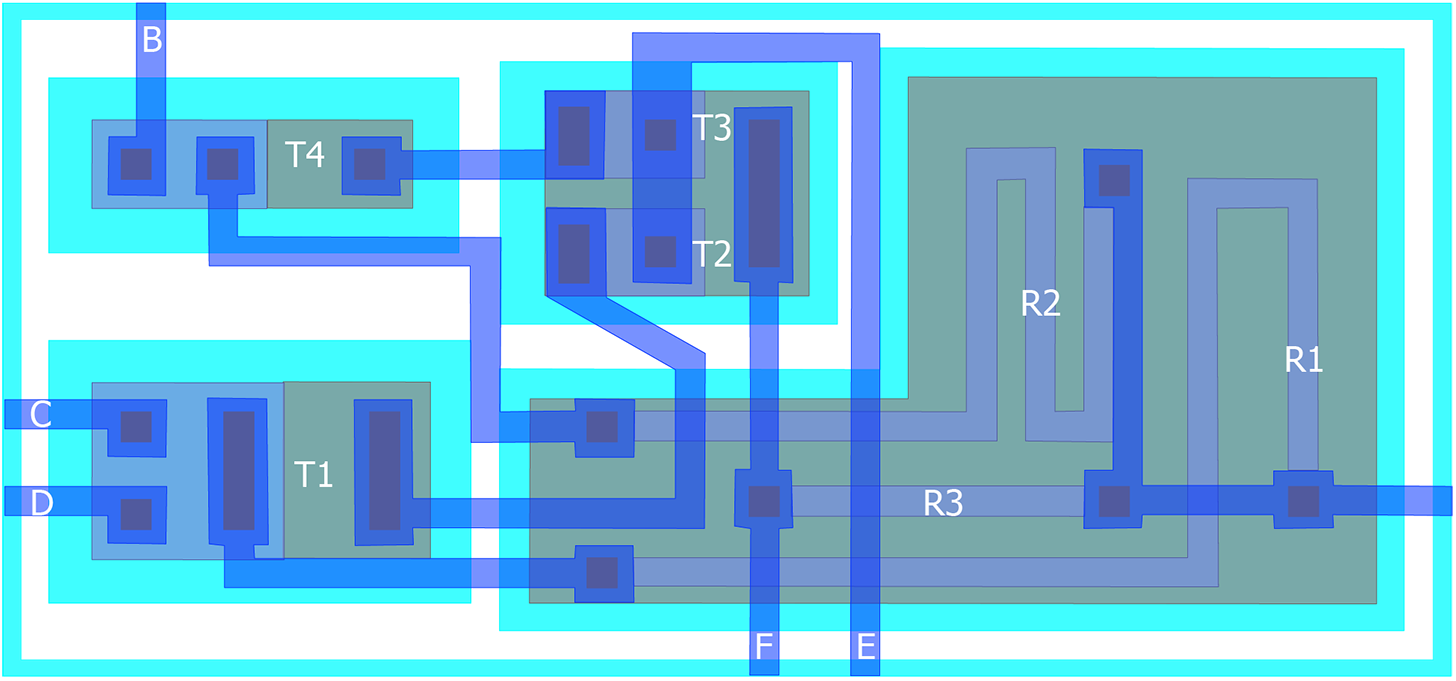

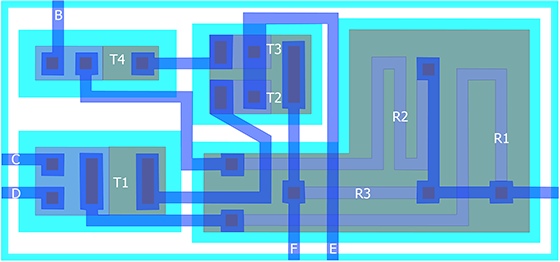

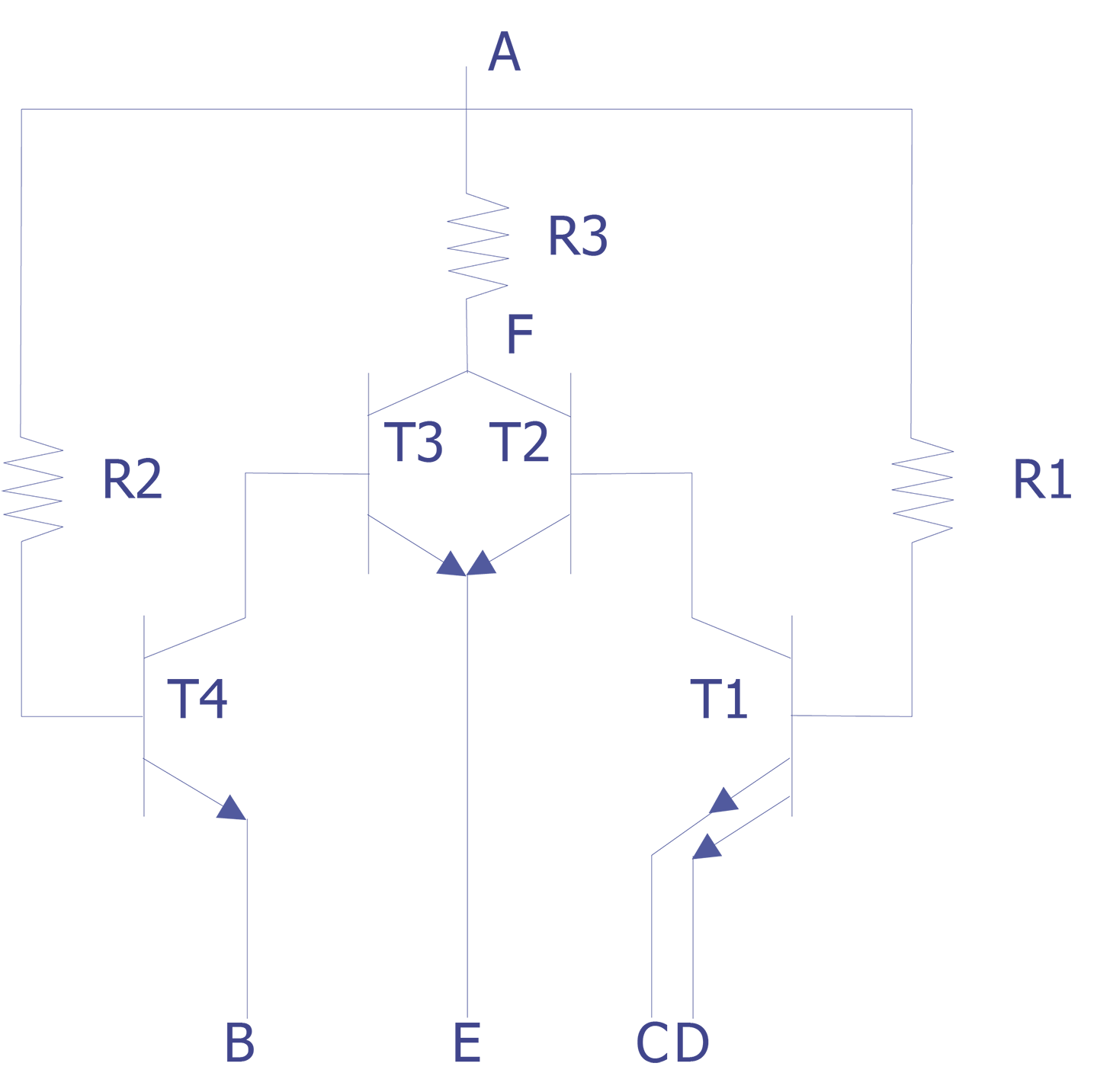

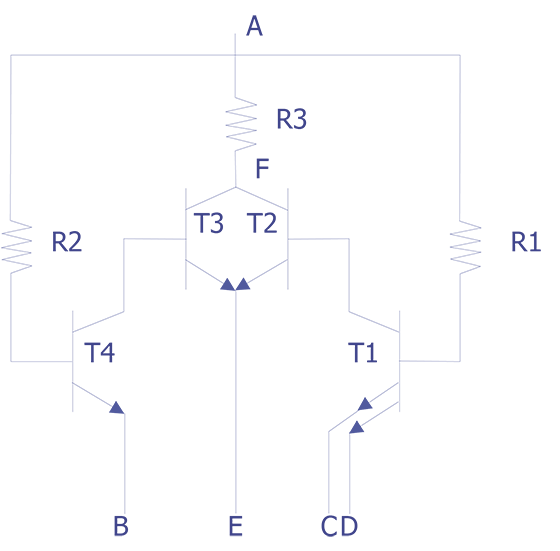

Next, we show a series of layouts demonstrating resistors in the bipolar process. Figure 4 shows an example of this.The following figure shows a series of layouts demostrating several npn and pnp transistors that are different in design than those shown in Figs. 1 through 3 (see Figure 5). Finally, a bipolar circuit exhibiting an R-S flip flop is shown in Figure 6. The schematic is shown in Figure 7. At this point, it is also worthwhile to show an oxide isolated bipolar process (see Figure 8). This process is more commonly used for today's bipolar circuitry because it eliminates the need for larger spacing between devices by using an oxide spacer between devices. The parasitic capacitances are also reduced, allowing the circuitry to switch faster.

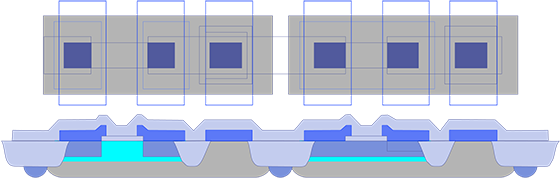

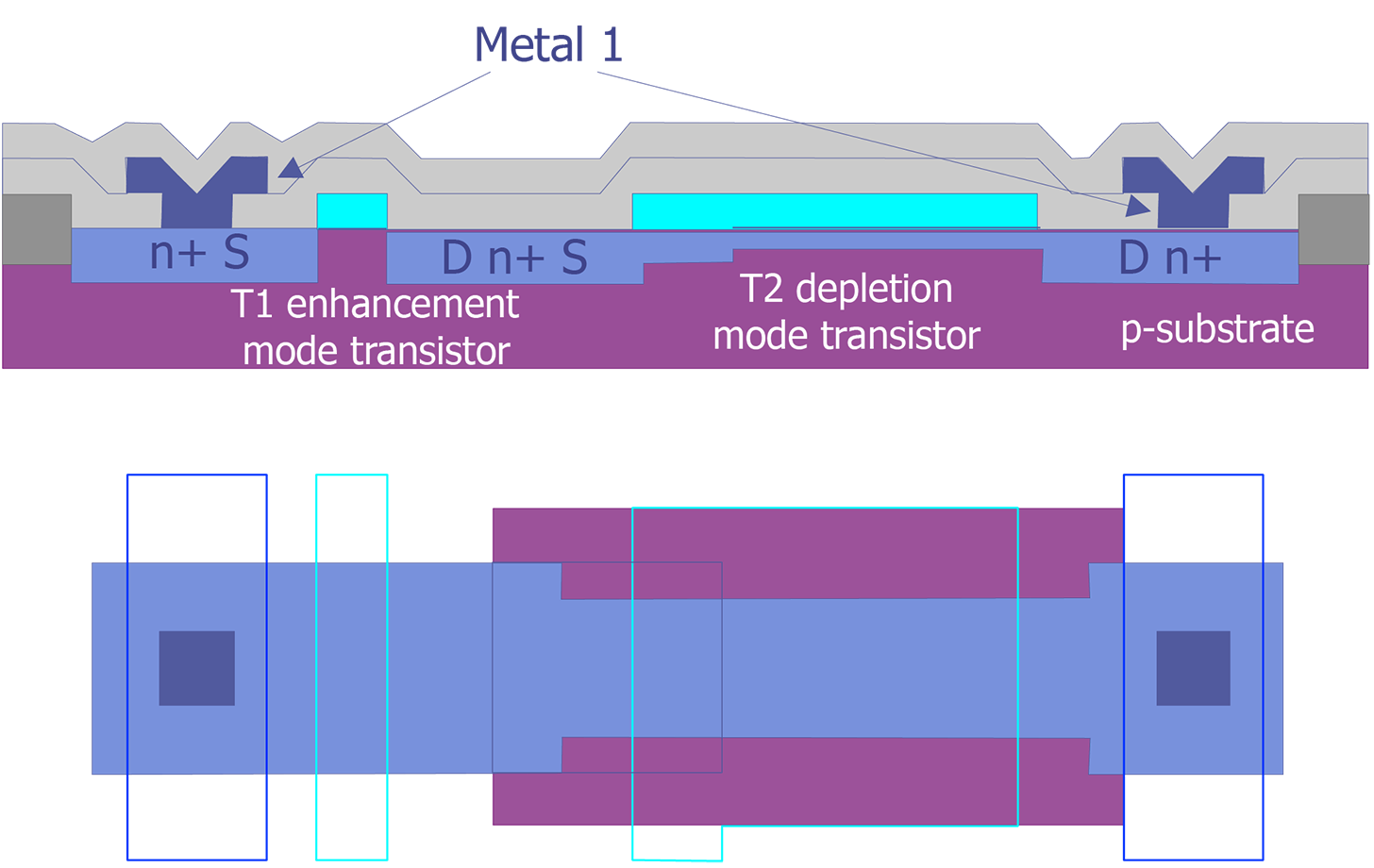

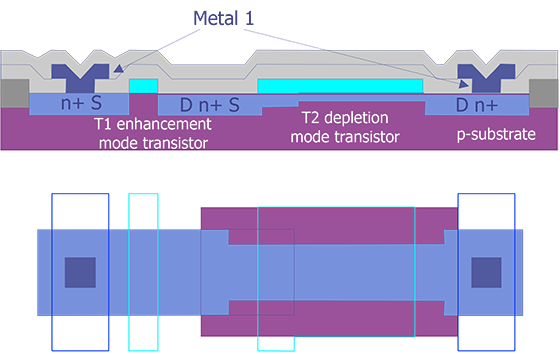

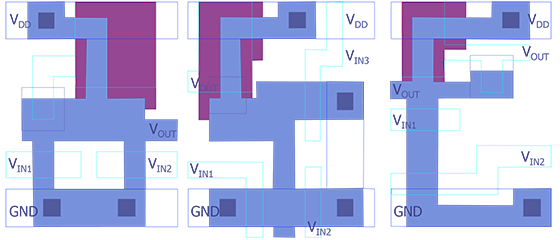

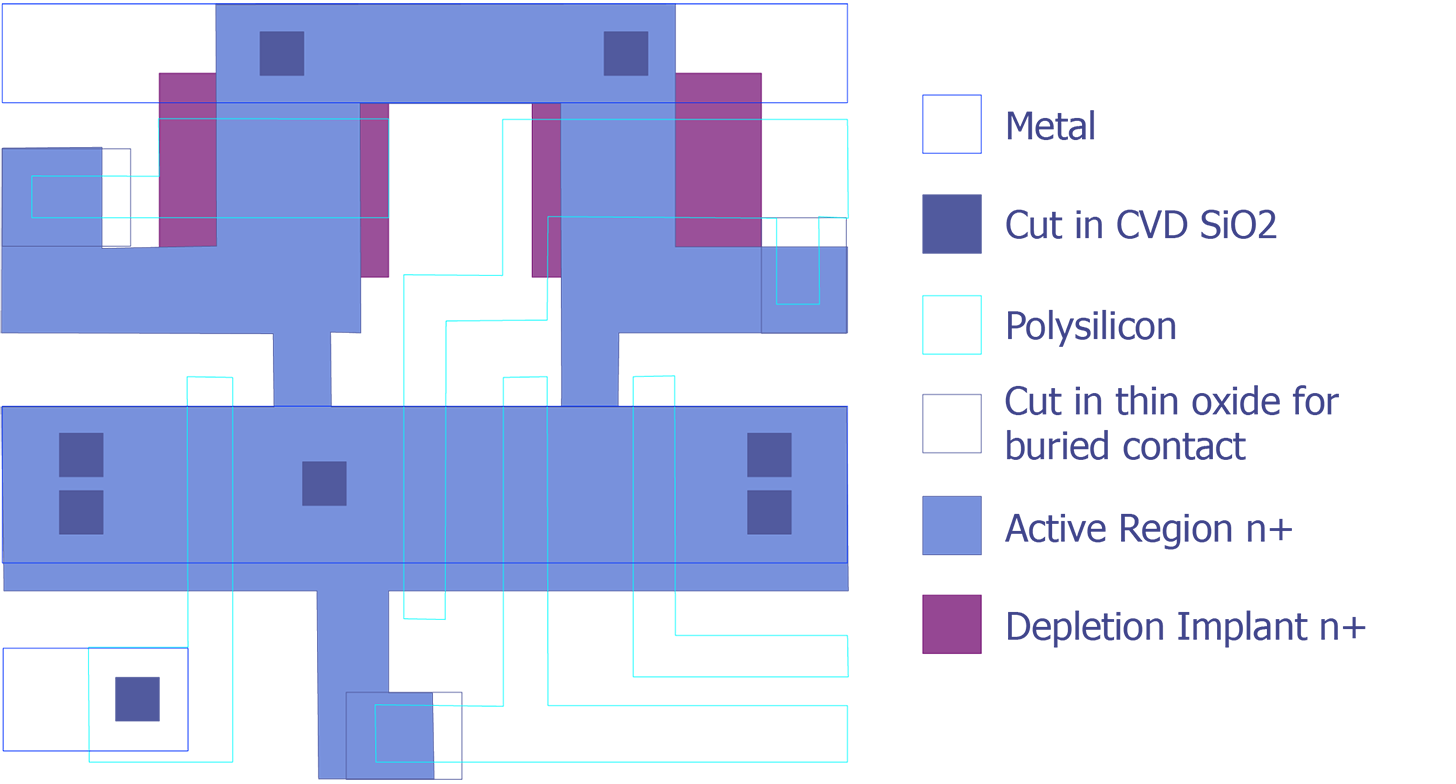

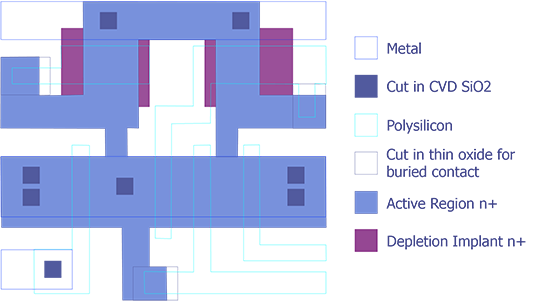

A typical NMOS process has the following appearance in cross section and top view (see Figure 9). The cross sectional and top view directly coincide in horizontal dimension so that you can see the relationship of various layers to structures in the top view. NMOS technology uses a depletion mode transistor as the pull-up transistor in an inverter structure. Next, a series of NMOS cells are shown, including a two input NOR gate, a three input NOR gate, a NAND gate (see Figure 10), and an RS flip-flop composed of cross-coupled NOR gates (see Figures 11a-11g).Figures 11a-11gFigures 11a-11gFigures 11a-11gFigures 11a-11gFigures 11a-11gFigures 11a-11g

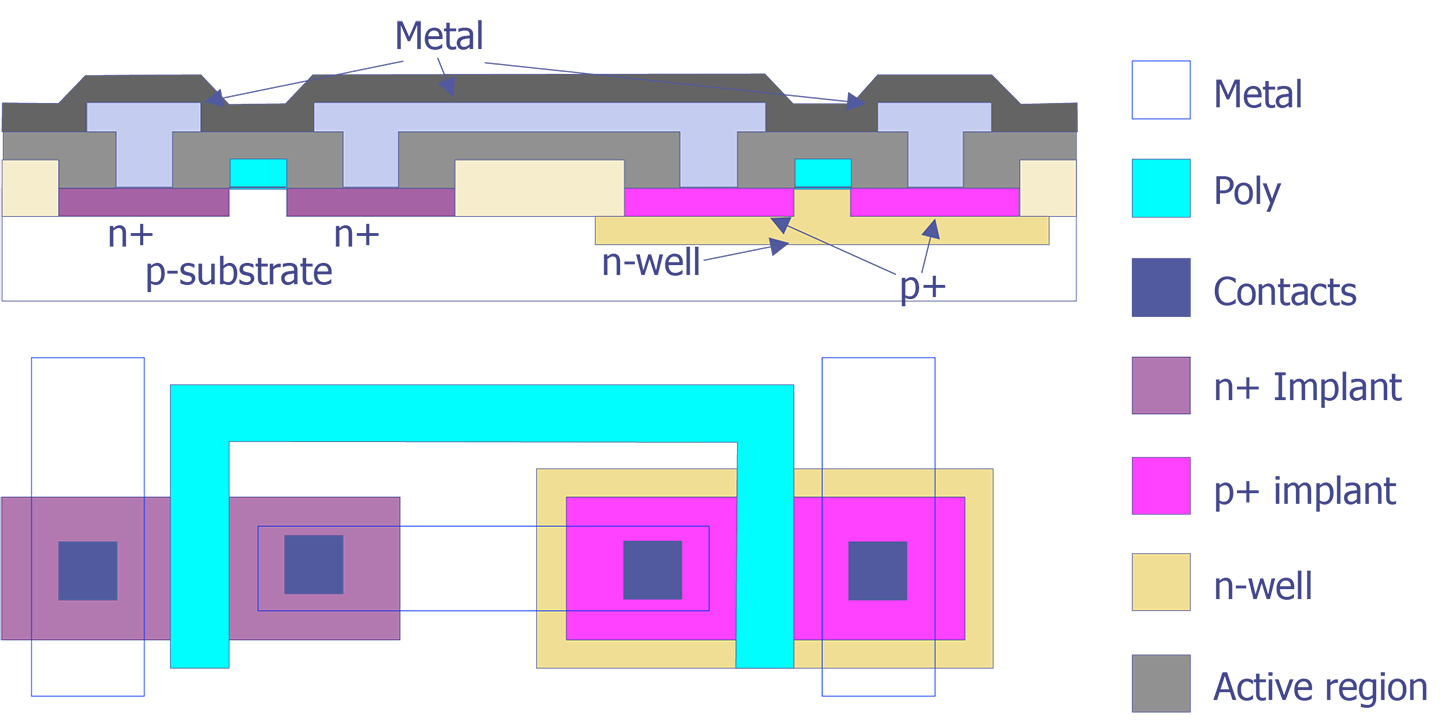

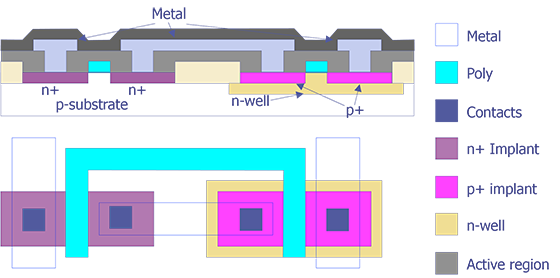

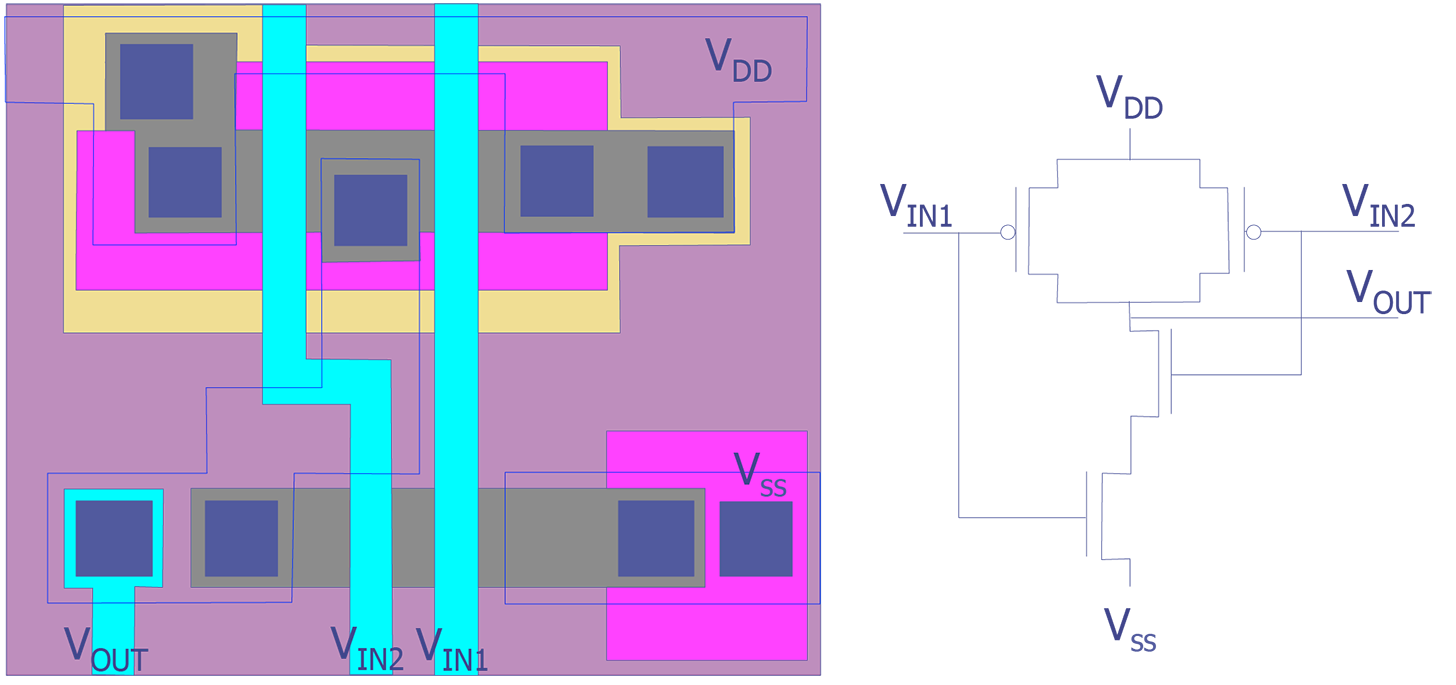

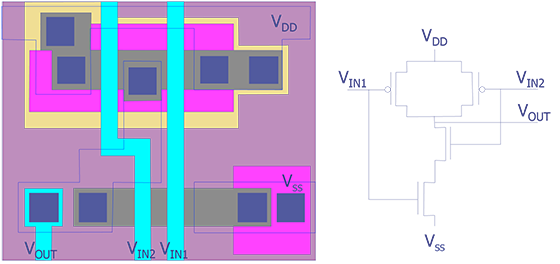

A typical n-well CMOS process has the following appearance in cross section and top view (see Figure 12). The cross-sectional and top view directly coincide in horizontal dimension so that you can see the relationship of various layers to structures in the top view. Next, we show a layout and schematic for a 2 input NAND gate (see Figure 13).

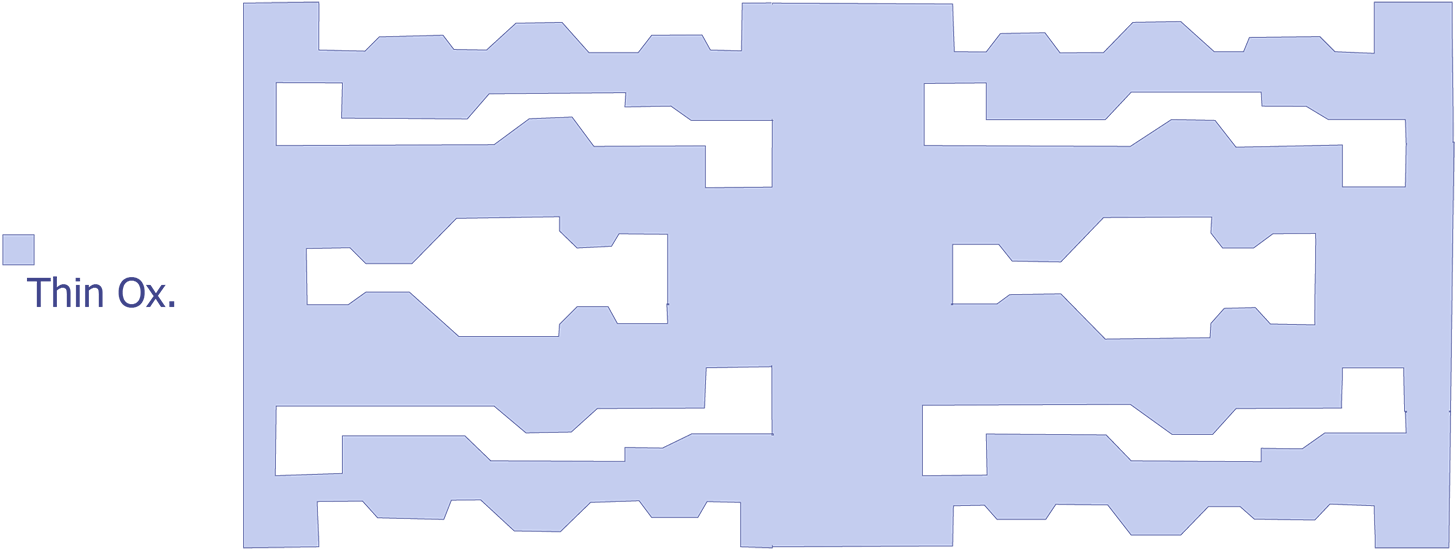

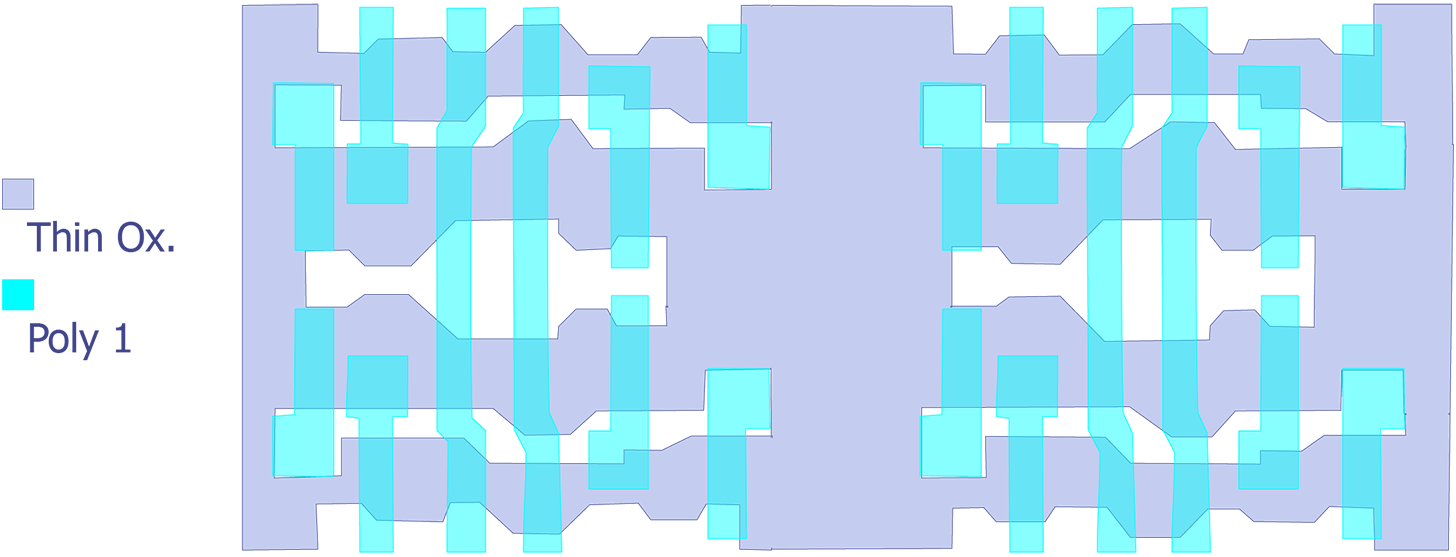

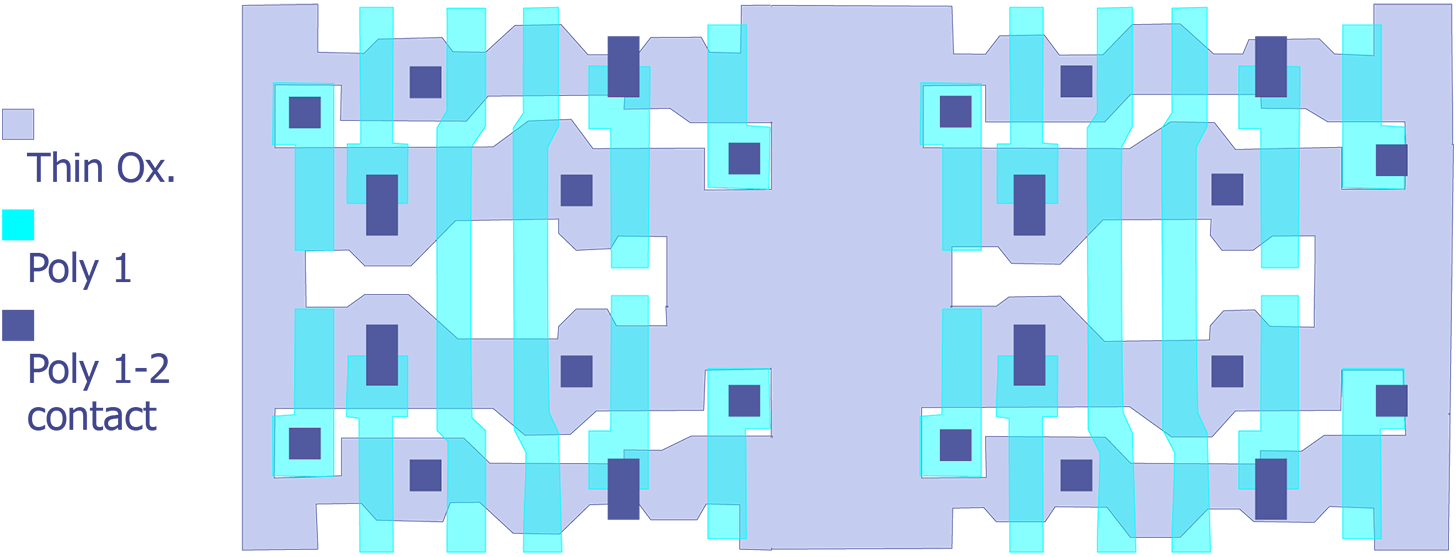

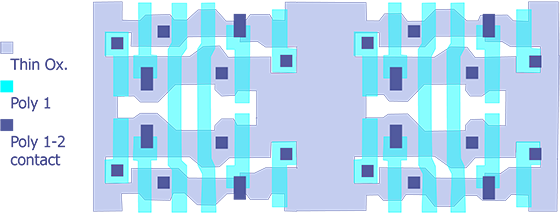

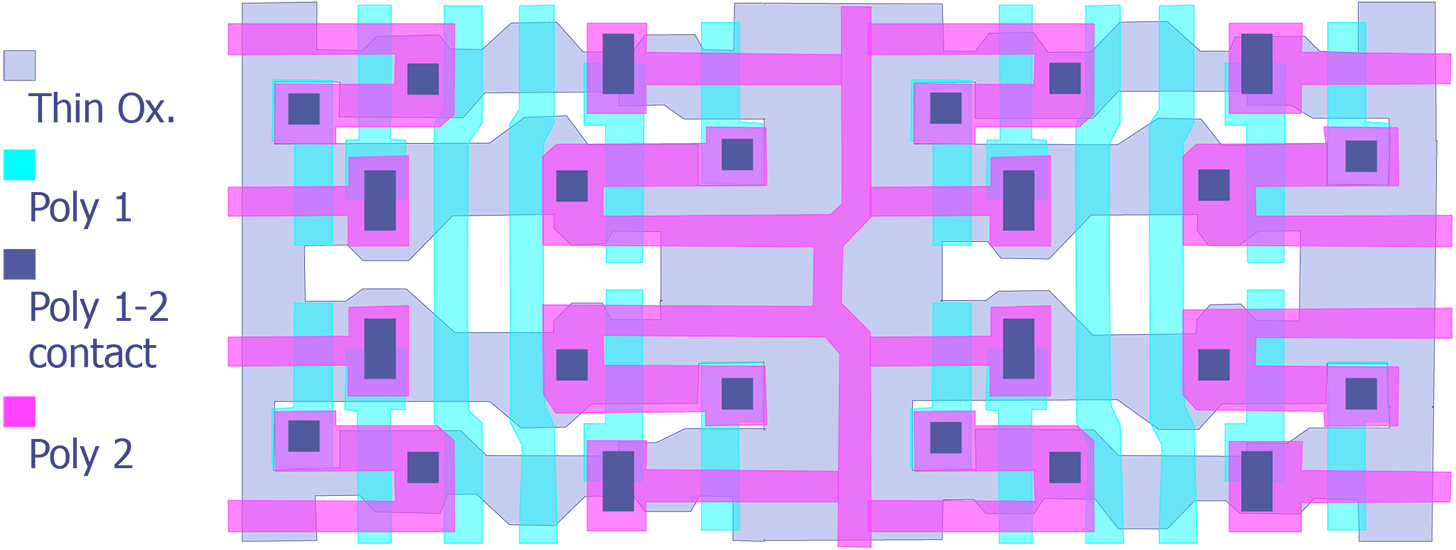

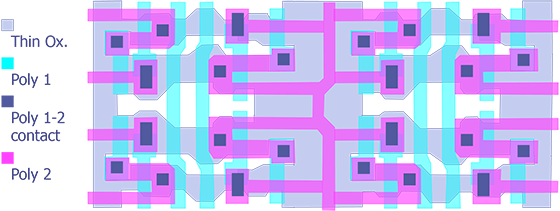

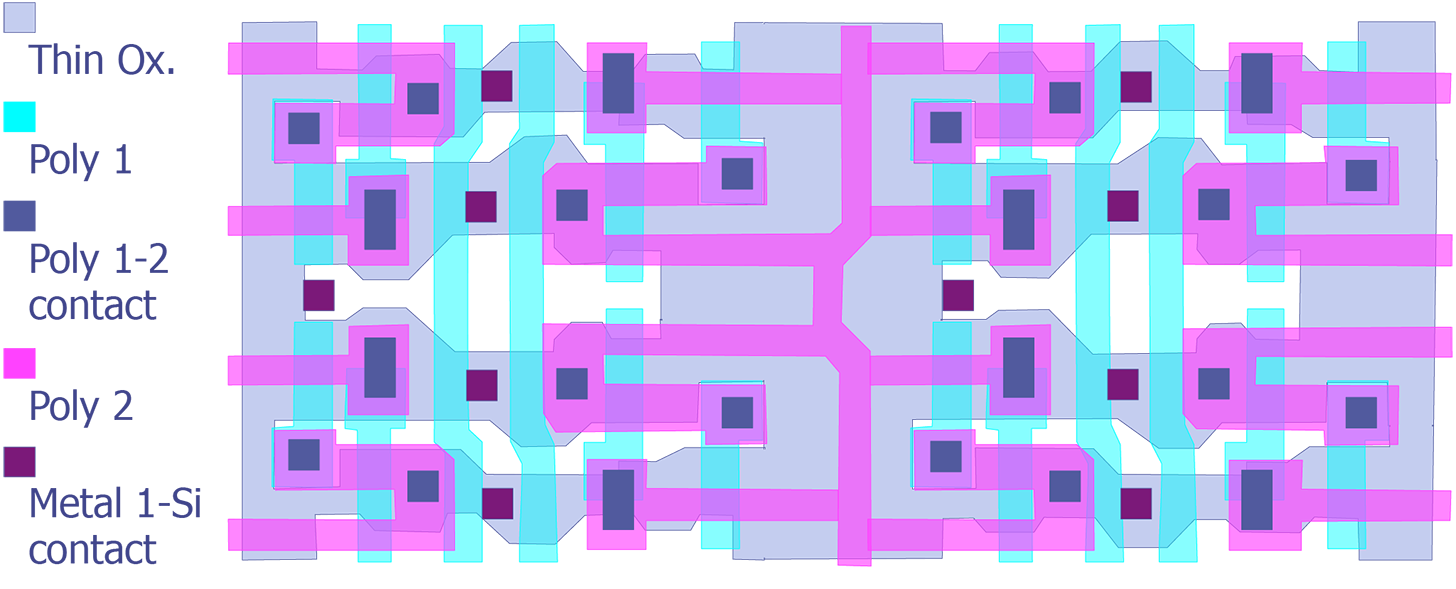

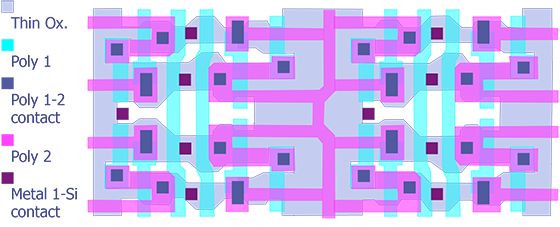

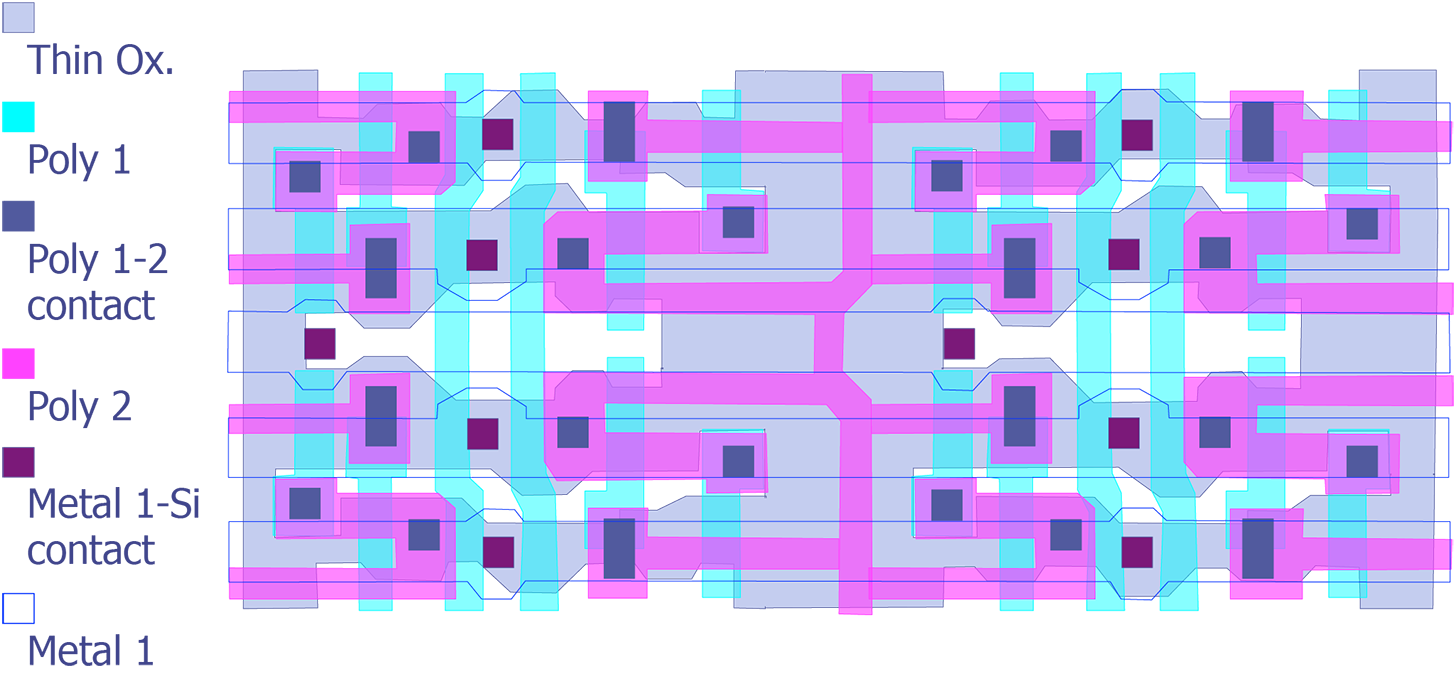

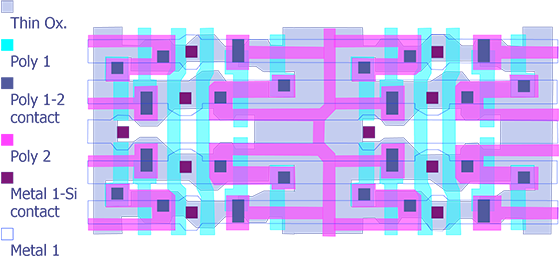

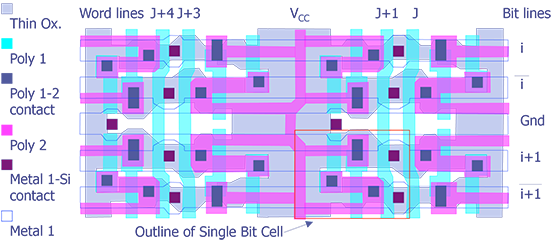

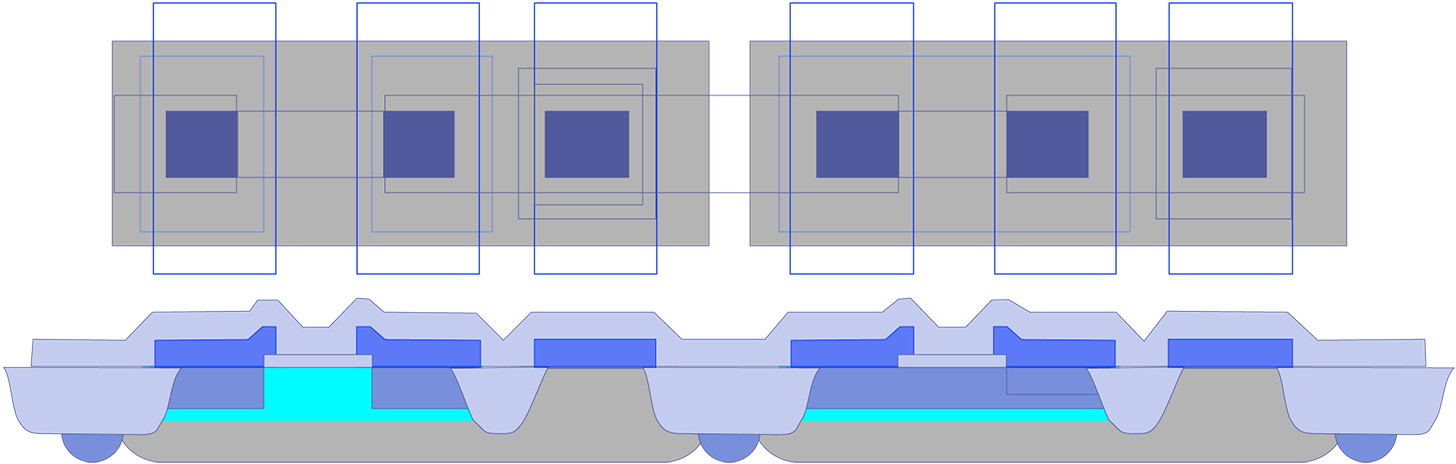

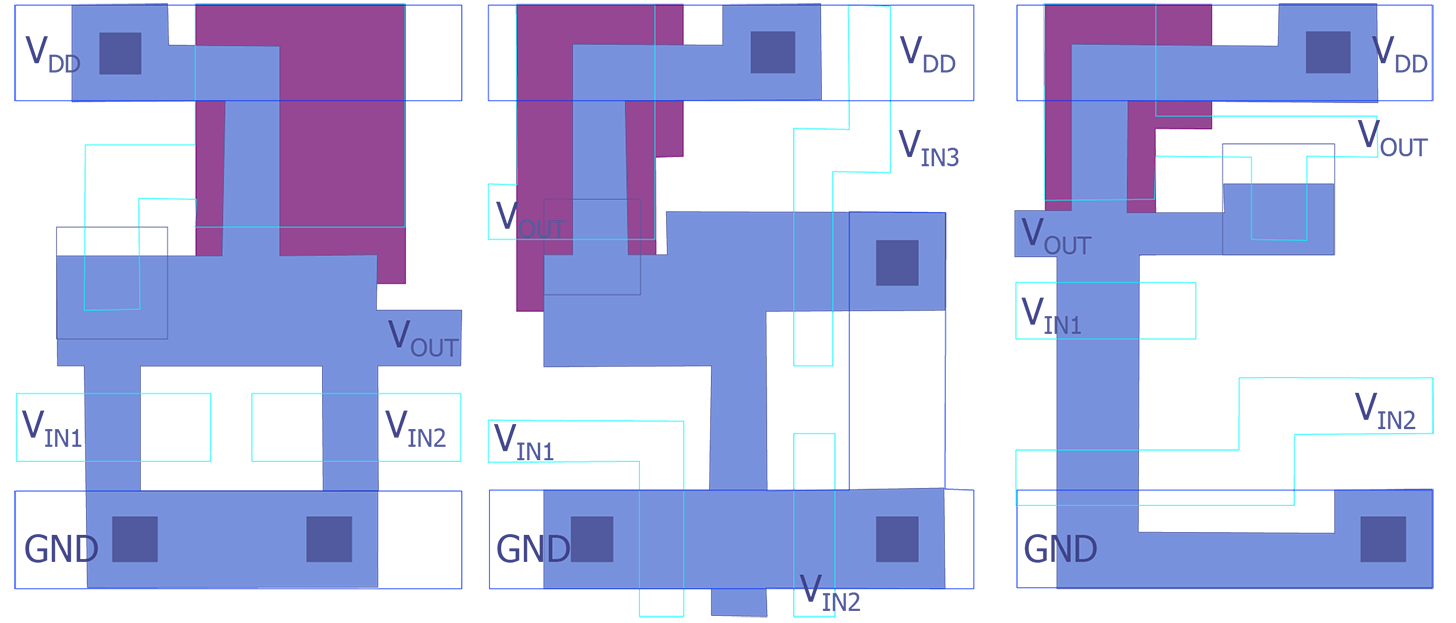

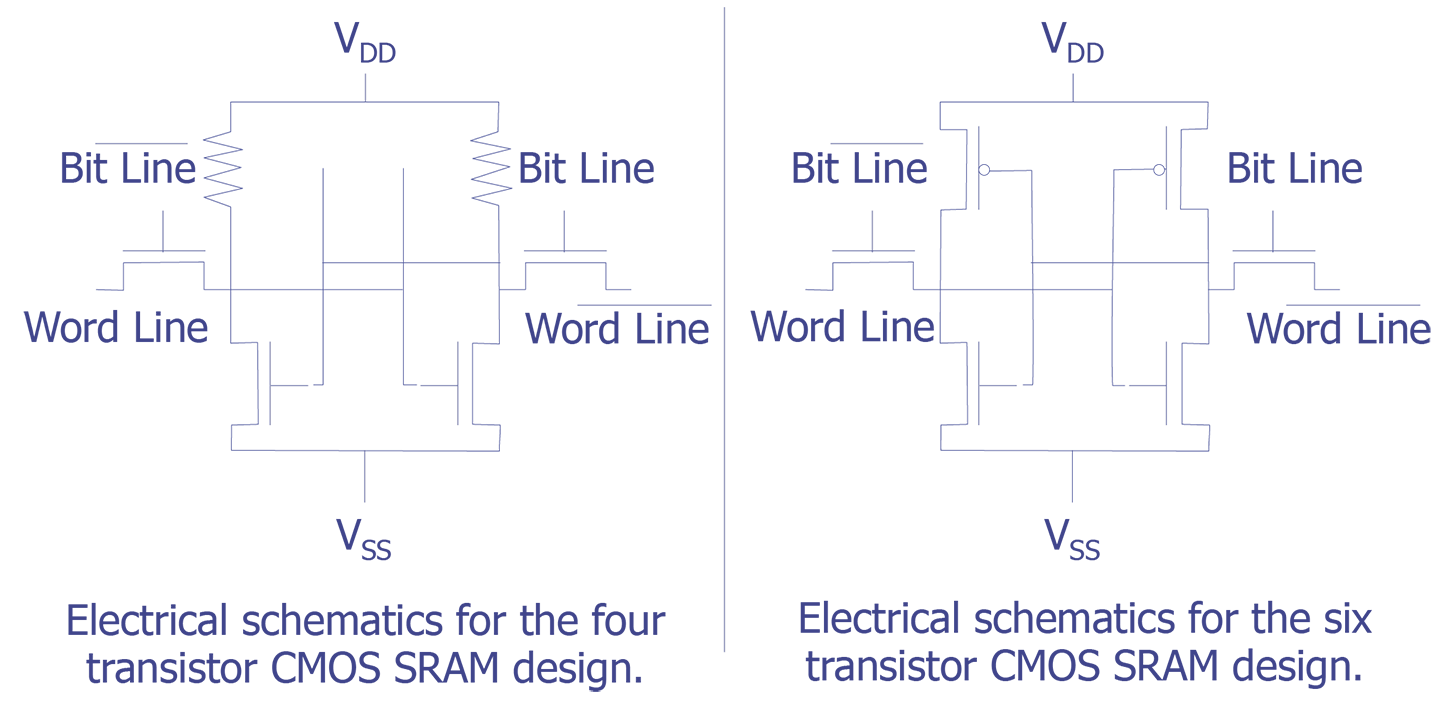

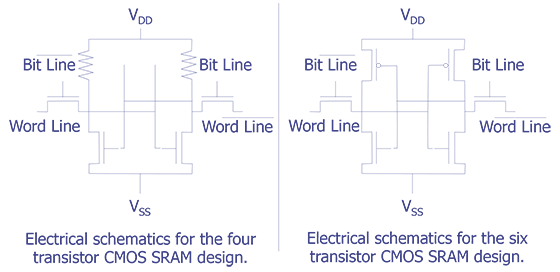

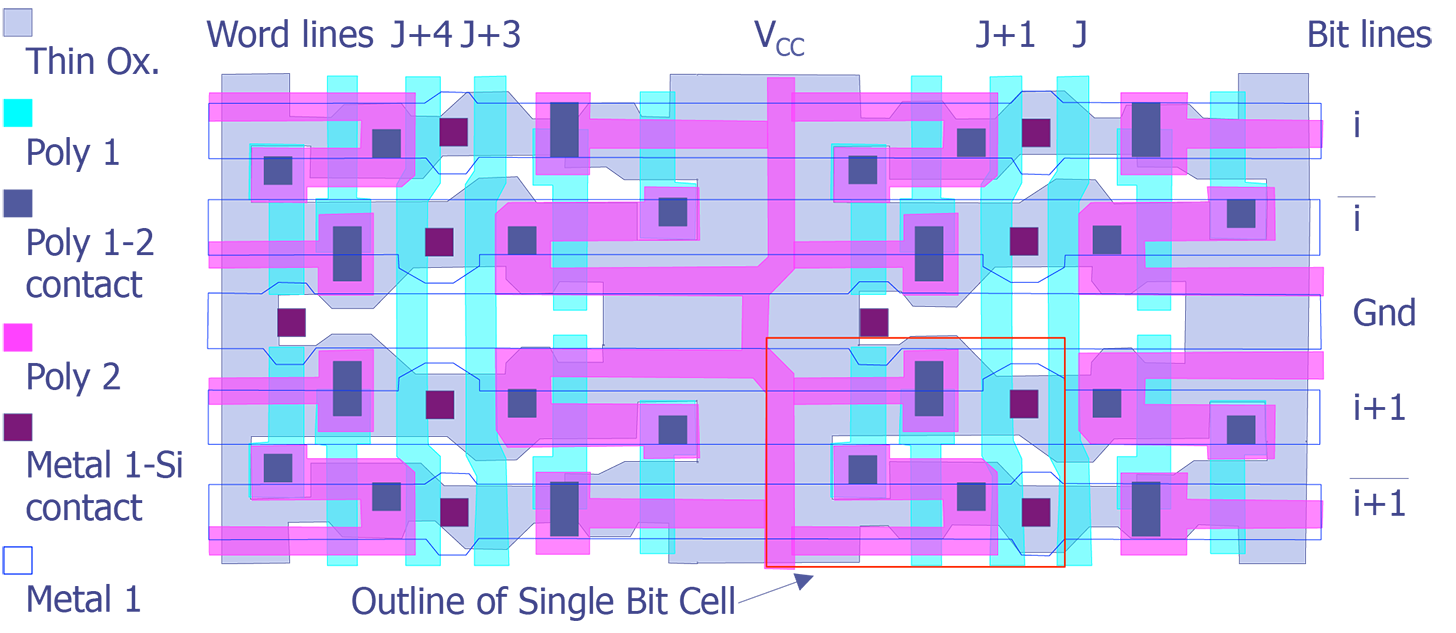

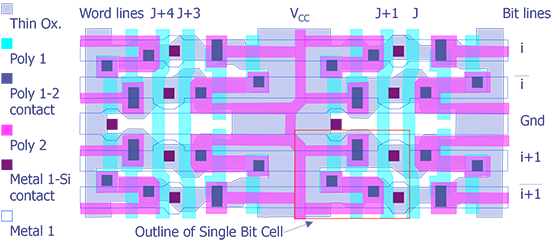

Now that we have examined the basic structures for bipolar, NMOS and CMOS technologies, let's examine memory structures. We will first discuss the CMOS Static Random Access Memory (SRAM). There are two major classes of design in CMOS SRAMs: the four transistor design and the six transistor design. Figure 14 shows both designs in electrical schematic format. Figure 15 shows the layout of the four transistor design. Figures 11a-11g show a step-by-step model of the patterning for this memory.Figures 11a-11gFigures 11a-11gFigures 11a-11gFigures 11a-11gFigures 11a-11gFigures 11a-11g

Device recognition is typically done once a suspect physical defect or layout abnormality is found. It is typically performed during optical examination with a high power microscope; however, the scanning electron microscope, scanning laser microscope and focused ion beam tools can also augment device recognition by providing higher quality or different contrast images. It may be necessary to perform the device recognition in two phases, one with all the metal layers intact and two with the IC stripped down to metal 1 or poly. If multiple ICs are available, this activity can proceed in parallel with other analysis activities.

If a significant amount of reverse engineering will be necessary to understand circuit operation, consult with the requestor and your management. Layout reverse engineering is very time consuming and should not be performed unless absolutely necessary.

Graphic sequence describing the major mask levels for a 4 transistor cell 64k Static Random Access Memory (SRAM) manufactured by Fairchild Semiconductor Research Center.